- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

I am using:

- Max10 10M40DAF256I7G

- Quartus 18.0

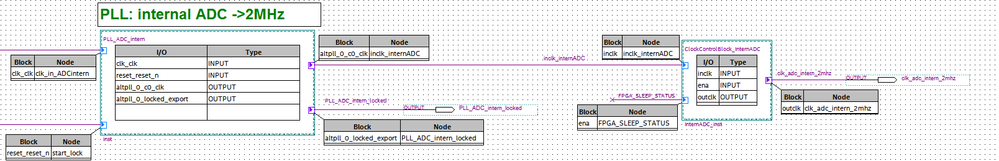

Here, I am using a PLL with 2MHz output (Intel ALTPLL) followed by ClockControlBlock which feeds the input of the Max10 internal ADC at the end (internal ADC is not shown and located at other .bdf File).

When compiling the whole project, the fitter sends out following error message:

Error (170084): Can't route signal "ClockPowerManager:inst..." to atom "TopLRFmain:inst1|CmdEx...rapper:adcblock_instance|primitive_instance"

At this point I can not find a problem and the RTL view shows that everything is connected until the internal ADC.

What else could be checked or is the route cause of such issue?

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It's hard to tell from what you posted because it just looks like the clock from the clock control block is just being fed to an output I/O pin. Can you provide the other schematic or what you see in the RTL viewer?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Take a look the following thread with a similar issue. Try some of the solutions mentioned in that and see if it resolves the issue.

https://forums.intel.com/s/question/0D50P00003yyROWSA2/error-170084-adc-pll

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Very good input Abe and I checked the solutions with my issue. Intel writes following statement to the ADC/PLL clock source (2.1.5 ug_m10_adc):

The ADC block uses the device PLL as the clock source. The ADC clock path is a dedicated clock path. You cannot change this clock path. Depending on the device package, the Intel MAX 10 devices support one or two PLLs—PLL1 only, or PLL1 and PLL3.

For devices that support two PLLs, you can select which PLL to connect to the ADC. You can configure the ADC blocks with one of the following schemes:

• Both ADC blocks share the same clock source for synchronization.

• Both ADC blocks use different PLLs for redundancy.

I use a dual ADC configuration with a single PLL for the ADC. The clock source to the ADC PLL is CLK1p (Pin K6) which is the input for PLL1 and PLL3 of the Max10. Below the input CLK1 with the PLL_ADC_intern and a ClockControlBlcok. The output goes to the Max10 dual ADC.

Question:

- Do I need to tell which PLL I am unsing for the ADC? According the Intel manual (see above) it says "you can select which PLL to connect to the ADC." Where can I do that?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

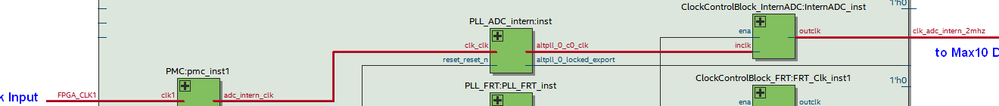

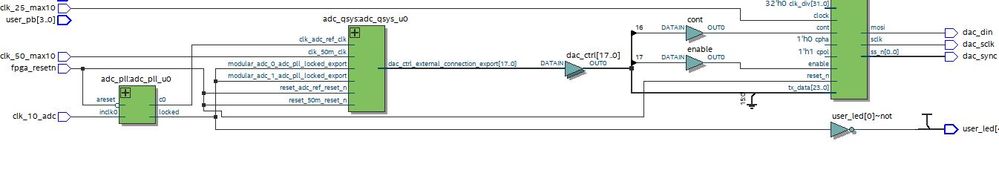

Why don't you try using Qsys yo build your Dual ADC system and then have a PLL external to the Qsys system as shown in this desgin. This simple Dual ADC design compiles without any issues.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

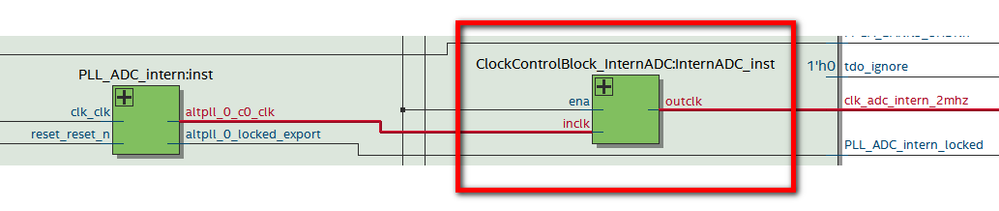

I think I have found the problem now. What I am using is a PLL followed by a Clock-ControlBlock which goes to the ADC. It looks like this:

When this Clock-ControlBlock is deleted it works. The reason for this Clock-ControlBlock is to disable the ADC PLL when not used.

Question:

- How would you enable/disable such ADC PLL Clock?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

nobody any idea how to use a Clock controlblock to disable the PLL ADC? As mentioned it does not work if the Clock controlblock is in between the PLL_ADC and the internal ADC of the Max10.

Thanks

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page