- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

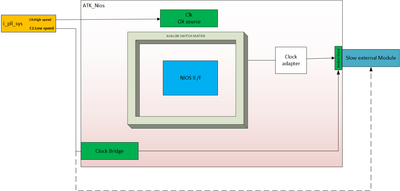

I am having a design philosophy question here. I would like to split my design in two categories: "high frequency/high speed" modules et "low frequency/low speed" modules on the NIOS II Avalon MM, in order to lighten up the constraints for the synthesis among others. I have a Clock bridge bringing the slow clock inside the NIOS (would it be better to use a "clock source" ?) and I have been connecting it to my slow clock modules following the clock crossing adapters view (added automatically during the generation).

I have one module which is outside of the NIOS and is needs to be clocked with the same slow clock entering the NIOS. What should be the best way to do it ?

- Connecting directly the external clock entering the NIOS to the Module ?

- Outing a clock from the NIOS ? and how ?

Thank you in advance for your help.

Tobias

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, that is what I was picturing. No, there is no difference or advantage in either setup. It's just wires.

If it was my design, I might just include the PLL in the Platform Designer system. That way, I could easily manage the connections to other components I might add to the system, adding an output clock bridge if needed, and making the whole thing more portable.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When you say "entering the Nios" or "inside the Nios", I presume you mean "entering the Platform Designer system" and that your box labeled "ATK_Nios" is your Platform Designer system.

First, the clock bridge and clock source components are basically identical. Clock source combines clock with reset. You can use either.

Are you saying that "slow external module" is outside of your Platform Designer system and you are exporting the Nios host (master) interface? If so, you can connect directly to the PLL like the dashed line you have or add an additional clock bridge to your Platform Designer system, exporting the output of that second bridge so the slow clock can be used both inside and outside the system.

I'm not sure if this is what you are looking for.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for you responses.

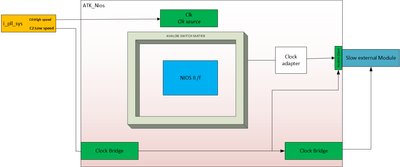

To be sure when you say: "add an additional clock bridge to your Platform Designer system, exporting the output of that second bridge so the slow clock can be used both inside and outside the system." Do you mean doing this ?

Would you recommend doing one rather than the other solution (connecting directly the PLL) ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, that is what I was picturing. No, there is no difference or advantage in either setup. It's just wires.

If it was my design, I might just include the PLL in the Platform Designer system. That way, I could easily manage the connections to other components I might add to the system, adding an output clock bridge if needed, and making the whole thing more portable.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you have any further questions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

No I think I have everything I need, thank you for your responses !

Tobias

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page