- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am new to the Altera Quartus software tool.So Please anyone guide me to accomplish my task.

Design Process involves:

1. Need to compile 8-bit, or 32-bit or 64-bit counter in Quartus

2. Interconnect the counter module with NIOS using SOPC

3. Want to see counter result in NIOS console

For above design, i Have followed the below step but in NIOS data is not printing in proper sequence (randomly printing). I dont know why ?

VERILOG code

SUB-MODULE

module counter

(

input clk, enable, rst_n,

output reg[7:0] count

);

always @ (posedge clk or negedge rst_n)

begin

if (~rst_n)

count <= 0;

else if (enable == 1'b1)

count <= count + 1;

end

endmodule module Counter_Top_Level_design

(

input clk,

input rst_n,

output [7:0] out

);

wire counter_enable;

counter counter_inst (

.clk ( clk ),

.rst_n ( rst_n ),

.enable ( counter_enable ),

.count ( out )

);

// For simulation, use this instantiation:

NIOS_SYSTEM niosii_system_inst (

.clk_clk ( clk ), // clk.clk

.reset_reset_n ( rst_n ), // reset.reset_n

.enable_external_connection_export ( counter_enable ), // output_pio.export

.cout_export ( out )

);

endmodule

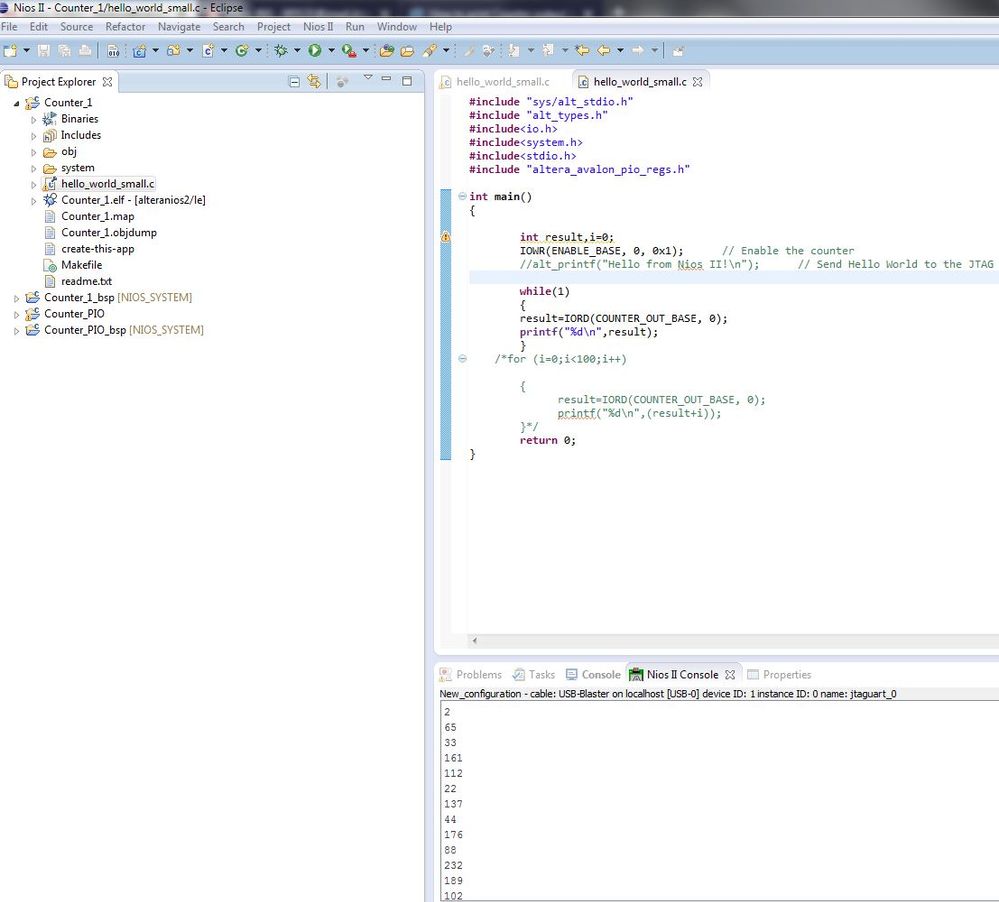

NIOS console

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

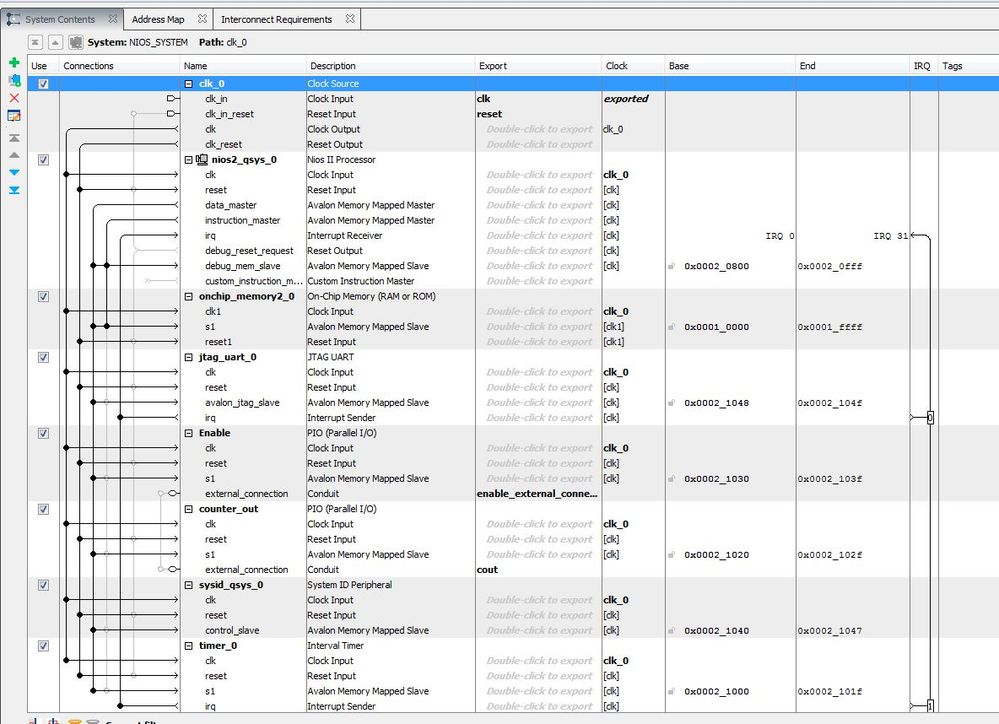

I have uploaded Qsys design too. Enable : PIO 1-bit (Output) and cout_export : PIO 8-bit Input

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Refer to your other post (please don't duplicate questions...)

https://forums.intel.com/s/question/0D50P000041tK2gSAE/how-to-print-counter-output-in-nios-console-

This behaviour is entirely expected. Your 'printf' statement will take thousands of clock cycles to complete. Meanwhile your 8-bit counter has wrapped many times giving you the appearance of a random output.

Increase your verilog counter size to 32-bit (along with your PIO input) and see what you get.

Cheers,

Alex

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

>>please don't duplicate questions...) Sorry 😪

>>Increase your verilog counter size to 32-bit (along with your PIO input) and see what you get.

I have followed your steps but same issue i am facing. I think AVALON FIFO memory will work it out. Can you help me in connection.

NIOS Screenshot for 32-BIT (attachment)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The change demonstrates exactly what I'm referring to. Your software loop takes 4336-1954=2382 clock cycles (of 'clk') to get around once. This is almost entirely down to the printf statement you have.

If you are expecting each printf to show an increment of 1 then you're not implementing something that will do that.

You need to explain what it is you're trying to do or what you're expecting.

Cheers,

Alex

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Counter design is my Initial/example design task. I want to print the counter data in NIOS Console.

My actual design Process starts as below

- I will generate Trigger signal in Quartus

- Based on that Trigger signal (500ns) i need to run the counter and collect the data in register. (In Quartus)

- Then i need to transfer the data from NIOS to PC through WIZNET 5300.

Its totally new task to me 😇 . Can you explain me the flow how i can accomplish this task .

Thanks in advance.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page