- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

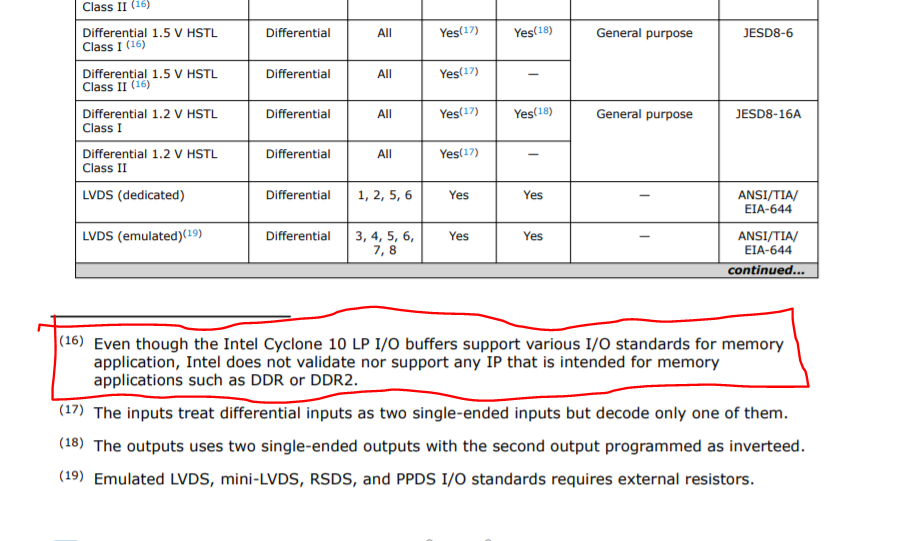

We know from the manual that cyclone 10 LP does not have DDR / DDR2 IP support. The customer needs DDR / DDR2 cache. From the Handbook, we can see that I / O of cyclone 10 LP supports DDR / DDR2 I / O standard

2 according to the previous device DDR2, the data cable must be connected to the pin with DQ pin name, while the pin name of cyclone 10 has no relevant description.

Please double confirm. If the cyclone 10 LP supports DDR & DDR2, do you have any special settings for the allocation of hardware pins, the description of relevant documents, and reference design

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear ANi,

Thank you for joining this Intel Community.

Please allow me to address and answer your questions as below.

- We know from the manual that Cyclone10 LP has no DDR/DDR2 IP support. The customer needs DDR/DDR2 cache. From the Handbook, we can see that Cyclone 10 LP I/O is I/O supporting DDR/DDR2. standard.

[Aida]: I am sorry to inform that Cyclone 10 LP device do not support any external memory interface (EMIF) IP. This also mentioned in C10 LP GPIO UG --> https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-10/c10lp-51003.pdf#page=77

If you want to use EMIF, you have to switch to Cyclone 10 GX. However, Cyclone 10 GX only support DDR3.

2. According to the previous device, the data line of DDR2 must be connected to the pin with the DQ pin name. The Cyclone 10 pin name has no relevant description.

[Aida]: The pins are assigned to allows fine tune of the phase shift for input clocks or strobes to properly align clock edges needed to capture data. This is not use-able for Cyclone 10 LP.

3. Please double-confirm, if Cyclone 10 LP supports DDR&DDR2,is there any special setting on the hardware pin assignment, whether there is a description of related documents, and Reference Design.

[Aida]: As per mentioned in no.1 above, EMIF IP including DDR/DDR2 is not supported in Cyclone 10 LP.

Referring to the pin assignment, you may refer to this C10 LP Pin Connection Guidelines for more details. Please note that these pin connection guidelines are provided as examples only, the use of the pin connection guidelines for any particular design should be verified for device operation with the applicable datasheet -->

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/dp/cyclone-10/pcg-01021.pdf

This is the pin-out files listing Intel FPGA device pin-out descriptions by Family for your reference. You may filter the desired device here.

--> https://www.intel.com/content/www/us/en/programmable/support/literature/lit-dp.html

I sincerely hope this helps. Let me know if I missed out anything. 😊

Thanks

Regards,

Aida

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page