- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

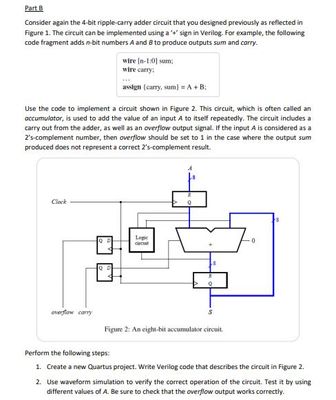

I have been trying to do the 8-bit accumulator as the picture attached below but can't get the desire waveform. Can anyone help me? Below are the Verilog HDL coding I had done :

module ripple_add(a, b, s, cout);

input [7:0] a,b;

output [7:0] s;

output cout;

wire c1, c2, c3, c4, c5, c6, c7;

fulladd fa0(a[0], b[0], 0, s[0], c1);

fulladd fa1(a[1], b[1], c1, s[1], c2);

fulladd fa2(a[2], b[2], c2, s[2], c3);

fulladd fa3(a[3], b[3], c3, s[3], c4);

fulladd fa4(a[4], b[4], c4, s[4], c5);

fulladd fa5(a[5], b[5], c5, s[5], c6);

fulladd fa6(a[6], b[6], c6, s[6], c7);

fulladd fa7(a[7], b[7], c7, s[7], cout);

endmodule

module acc (a, sum ,overflow, clk, carry);

input [7:0] a;

input clk;

output reg overflow;

output wire carry;

output wire [7:0] sum;

reg d1,d2,b;

reg [7:0]r1,r2;

ripple_add add(.a(a),.b(r2));

assign {carry,sum} = a+r2;

always @(posedge clk)

begin

if (sum==a)

overflow = 0;

else

overflow =1;

end

always@(posedge clk )

begin

r1=a;

r2=sum;

d1<=overflow;

d2<=carry;

end

endmodule Thanks a lot if anyone willing to help me on this.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

fulladd is missing. Could you share the full design QAR and testbench for investigation? To generate the QAR file, click on Project > Archive Project

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is the QAR file. I have provided a full picture and requirements in the picture also.

if there is still can't find the fulladd, here is the code for it:

module fulladd(a, b, cin, s, cout);

input a, b, cin;

output s, cout;

assign s = a ^ b ^ cin;

assign cout = ((a ^ b) & cin) | (a & b);

endmodule

I didn't do any testbench for this design. But this is the waveform I got.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may find the acc.qar attached. Do let me know if this is not the intended design.

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We do not receive any response from you to the previous question/reply/answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page