- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello,

I am building a SOC project in platform designer with ARM HPS connected EMIF. The project got synthesized Successfully But I got error in Fitter.

I am using Han Pilot Platform (aria10 SOC) and intel quartus prime standard 18.

I have configured EMIF to use 4GB SODIMM RAM as memory for HPS. I am getting the following errors.

Error (14566): The Fitter cannot place 1 periphery component(s) due to conflicts with existing constraints (1 ADDR_CMD_GRP(s)). Fix the errors described in the submessages, and then rerun the Fitter. The Intel FPGA Knowledge Database may also contain articles with information on how to resolve this periphery placement failure. Review the errors and then visit the Knowledge Database at https://www.altera.com/support/support-resources/knowledge-base/search.html and search for this specific error message number.

Error (175020): The Fitter cannot place logic ADDR_CMD_GRP that is part of Arria 10 External Memory Interfaces for HPS a10s_ghrd_altera_emif_a10_hps_181_lhjxj5y in region (148, 87) to (148, 99), to which it is constrained, because there are no valid locations in the region for logic of this type.

Info (14596): Information about the failing component(s):

Info (175028): The ADDR_CMD_GRP name(s): a10s_ghrd:u0|a10s_ghrd_altera_emif_a10_hps_181_lhjxj5y:emif_a10_hps|a10s_ghrd_altera_emif_arch_nf_181_m5khxbq:arch|a10s_ghrd_altera_emif_arch_nf_181_m5khxbq_top:arch_inst|altera_emif_arch_nf_io_tiles_wrap:io_tiles_wrap_inst|altera_emif_arch_nf_io_tiles:io_tiles_inst|tile_gen[1].tile_ctrl_inst_ADDR_CMD_GRP_3

Error (16234): No legal location could be found out of 2 considered location(s). Reasons why each location could not be used are summarized below:

Error (175005): Could not find a location with: ADDR_CMDx3 (1 location affected)

Info (175029): ADDR_CMD_GRP containing Y5

Error (175005): Could not find a location with: HPS_AC (1 location affected)

Info (175029): ADDR_CMD_GRP containing Y5

Info (175015): The I/O pad DDR4A_CK is constrained to the location PIN_AD3 due to: User Location Constraints (PIN_AD3)

Info (14709): The constrained I/O pad is contained within a pin, which is contained within this ADDR_CMD_GRP

Error (15307): Cannot apply project assignments to the design due to illegal or conflicting assignments. Refer to the other messages for corrective action.

Error (16297): An error has occurred while trying to initialize the plan stage.

Error: Quartus Prime Fitter was unsuccessful. 8 errors, 1411 warnings

Error: Peak virtual memory: 7262 megabytes

Error: Processing ended: Mon Sep 06 17:48:24 2021

Error: Elapsed time: 00:00:42

Error: Total CPU time (on all processors): 00:00:41

Error (293001): Quartus Prime Flow was unsuccessful. 9 errors, 1996 warnings

Error (14566): The Fitter cannot place 1 periphery component(s) due to conflicts with existing constraints (1 ADDR_CMD_GRP(s)). Fix the errors described in the submessages, and then rerun the Fitter. The Intel FPGA Knowledge Database may also contain articles with information on how to resolve this periphery placement failure. Review the errors and then visit the Knowledge Database at https://www.altera.com/support/support-resources/knowledge-base/search.html and search for this specific error message number.

Error (175020): The Fitter cannot place logic ADDR_CMD_GRP that is part of Arria 10 External Memory Interfaces for HPS a10s_ghrd_altera_emif_a10_hps_181_lhjxj5y in region (148, 87) to (148, 99), to which it is constrained, because there are no valid locations in the region for logic of this type.

Info (14596): Information about the failing component(s):

Info (175028): The ADDR_CMD_GRP name(s): a10s_ghrd:u0|a10s_ghrd_altera_emif_a10_hps_181_lhjxj5y:emif_a10_hps|a10s_ghrd_altera_emif_arch_nf_181_m5khxbq:arch|a10s_ghrd_altera_emif_arch_nf_181_m5khxbq_top:arch_inst|altera_emif_arch_nf_io_tiles_wrap:io_tiles_wrap_inst|altera_emif_arch_nf_io_tiles:io_tiles_inst|tile_gen[1].tile_ctrl_inst_ADDR_CMD_GRP_3

Error (16234): No legal location could be found out of 2 considered location(s). Reasons why each location could not be used are summarized below:

Error (175005): Could not find a location with: ADDR_CMDx3 (1 location affected)

Info (175029): ADDR_CMD_GRP containing Y5

Error (175005): Could not find a location with: HPS_AC (1 location affected)

Info (175029): ADDR_CMD_GRP containing Y5

Info (175015): The I/O pad DDR4A_CK is constrained to the location PIN_AD3 due to: User Location Constraints (PIN_AD3)

Info (14709): The constrained I/O pad is contained within a pin, which is contained within this ADDR_CMD_GRP

Error (15307): Cannot apply project assignments to the design due to illegal or conflicting assignments. Refer to the other messages for corrective action.

Error (16297): An error has occurred while trying to initialize the plan stage.

Error: Quartus Prime Fitter was unsuccessful. 8 errors, 1411 warnings

Error: Peak virtual memory: 7262 megabytes

Error: Processing ended: Mon Sep 06 17:48:24 2021

Error: Elapsed time: 00:00:42

Error: Total CPU time (on all processors): 00:00:41

Error (293001): Quartus Prime Flow was unsuccessful. 9 errors, 1996 warnings

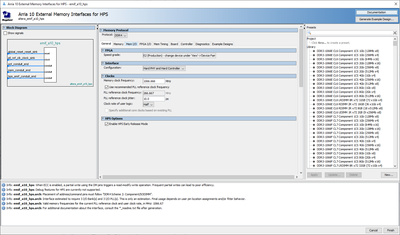

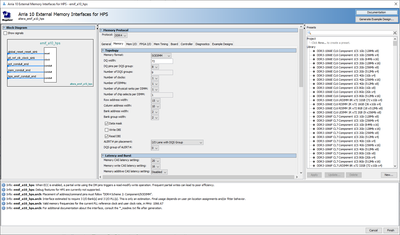

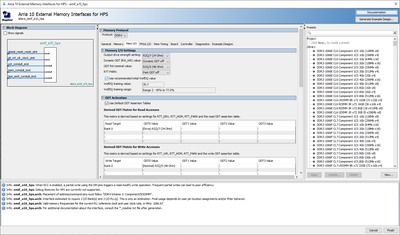

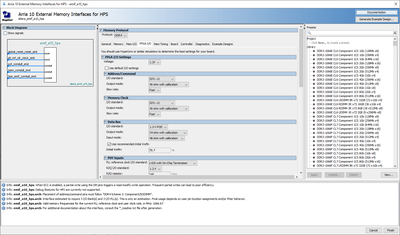

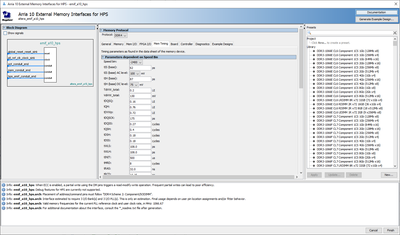

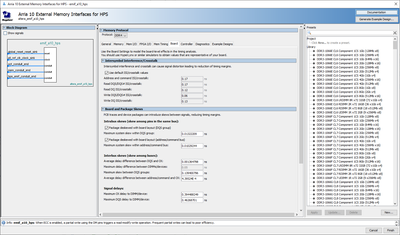

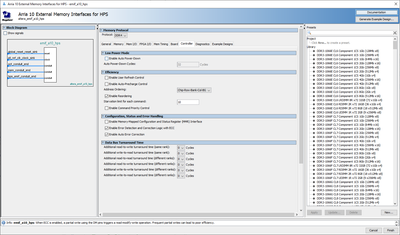

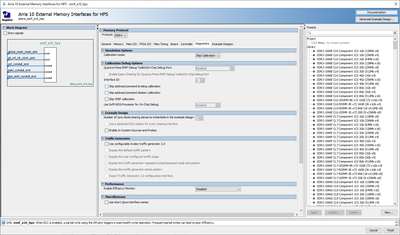

Screenshot of the EMIF IP configuration is attached here for reference.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For an Arria 10 SoC device, there is a very specific I/O bank you have to use for the EMIF for the HPS. I forget which one it is right now but remember that for HPS EMIF, it uses the same hardware as if you were adding an EMIF without the HPS. Thus, if you've located anything in the dedicated I/O bank that is required for the HPS EMIF, you'll get a no-fit like this. If you're using Quartus Prime Pro, you can use the Interface Planner to find the legal location for this EMIF. If you're using Standard, check the device user guide to find where the EMIF has to go and check in the Pin Planner if something is interfering.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you try below KDB:

https://www.intel.com/content/www/us/en/support/programmable/articles/000074695.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I HAVE EXACT SAME ISSUE , WHILE USING AN AGILEX DEVICE. IS THERE ANY RESOLUTION FOR THIS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Try to connect the clock to global signal maybe?

in .qsf:

set_instance_assignment -name GLOBAL_SIGNAL GLOBAL_CLOCK -to DDR4A_CK

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page