- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

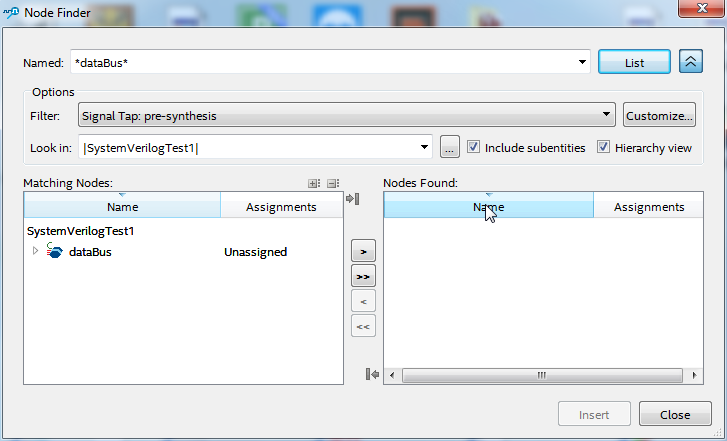

Hi. I'm struggling to debug certain parts of my design. I've been dancing around a data bus with SignalTap for the past few weeks but I really need to see what is on my dataBus element.

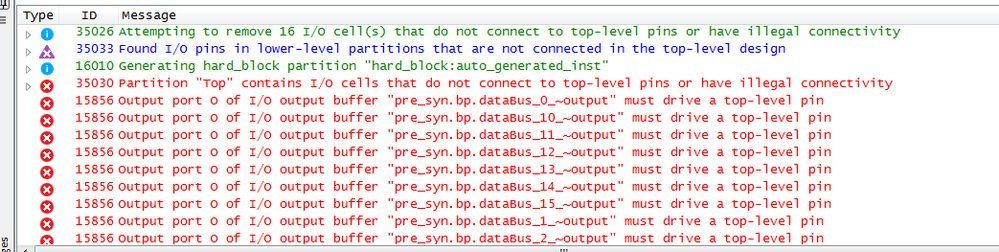

My project compiles fine until I dry to add dataBus to SignalTap.

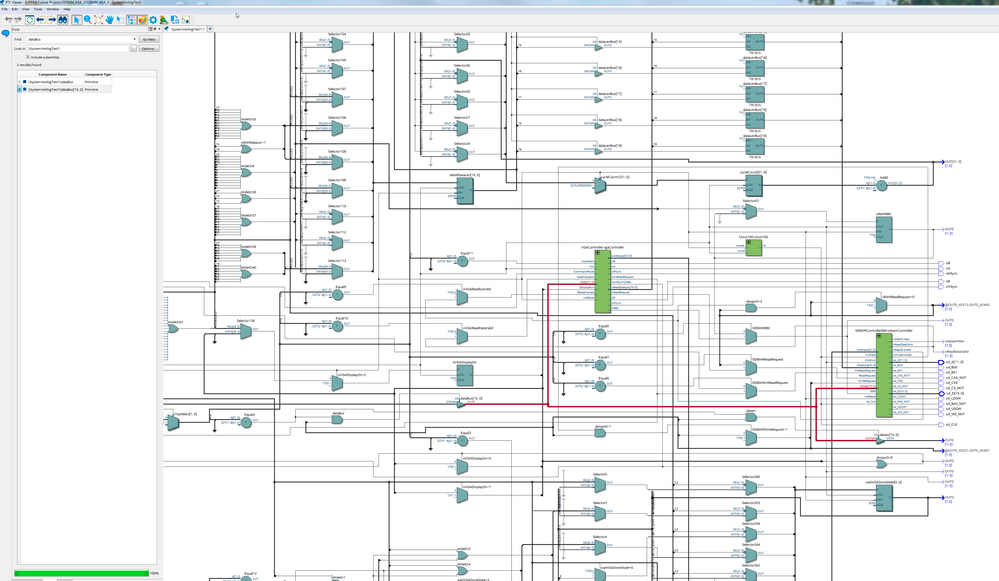

Here's the RTL Viewer showing dataBus:

Am I adding dataBus incorrectly within SignalTap? Should I be using something other than pre-synthesis?

I just want to know what I am doing wrong so I can monitor/debug this element of the design.

I've attached my project.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't think this has anything to do with Signal Tap. It looks like you've defined dataBus (called ioData in SDRAMController8Bit) as bidirectional logic. You can't use bidirectional logic for an internal signal. So the error is indicating that it needs to be connected to a pin, which is the only part of the device where bidirectional/tri-state logic exists.

This worked maybe without Signal Tap because the bidi logic could get optimized away. However, when you tie it to Signal Tap, it can't get optimized away so the error occurs. (Guessing; I didn't try compiling your project)

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't think this has anything to do with Signal Tap. It looks like you've defined dataBus (called ioData in SDRAMController8Bit) as bidirectional logic. You can't use bidirectional logic for an internal signal. So the error is indicating that it needs to be connected to a pin, which is the only part of the device where bidirectional/tri-state logic exists.

This worked maybe without Signal Tap because the bidi logic could get optimized away. However, when you tie it to Signal Tap, it can't get optimized away so the error occurs. (Guessing; I didn't try compiling your project)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for that. It's quite funny - I originally had in and out databuses on my internal components. I began to change them to single bidirectional buses thinking that's the way it should be in "real world" (oldschool external) logic. I didn't actually realise that bidirectional buses weren't possible. I had read the fact somewhere on a forum but I was in disbelief after seeing example Verilog code somewhere.

Right, well that changes a few things fundamentally and hopefully that explains why I've been having so many problems in general.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Paul,

Any other concern regarding this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page