- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Observing an error in quartus,

Info: *******************************************************************

Info: Running Quartus Prime Synthesis Info: Version 18.0.0 Build 219 04/25/2018 Patches 0.06 SJ Pro Edition

Info: Processing started: Wed Mar 25 05:18:11 2020

Info: Command: quartus_syn --read_settings_files=on --write_settings_files=off for_generate -c for_generate Info: qis_default_flow_script.tcl version: #1

Info: Initializing Synthesis... Info: Project = "for_generate"

Info: Revision = "for_generate" Info: Analyzing source files

Critical Warning(13432): Verilog HDL Compiler Directive warning at for_gen.sv(19): text macro "ONE" is undefined

Error(13411): Verilog HDL syntax error at for_gen.sv(19) near text ; Error(13363): Verilog HDL error at for_gen.sv(23): module "for_gen" ignored due to previous errors

Error: Flow failed: Error: Quartus Prime Synthesis was unsuccessful. 3 errors, 1 warning

Code:

module for_gen

#(parameter SIZE = 8) ( input [SIZE-1:0] gray, output [SIZE-1:0] bin ); localparam bit ON=1'b0;

genvar gi; // generate and endgenerate is optional generate

for (gi=0; gi<SIZE; gi=gi+1) begin : genbit

if(ON == 1'b1) begin

assign bin[gi] = ^gray[SIZE-1:gi]; // Thanks Dhruvkumar! end else begin assign bin[gi] = `ONE;

end

end

endgenerate

endmodule

I have declared `ONE in one of the include file and its part of project added in qsf as

set_global_assignment -name VERILOG_INCLUDE_FILE "/nfs/site/disks/dcsg_0041/sumukhbn/for_generate/include/for_gen_inc.vh"

But why still I am seeing this error?

Please resolve as soon as possible

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think you need a `include in your code. The assignment includes the file in your Quartus project but I don't think that lets your for_gen code refer to it.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't want add `include, because design is huge its very difficult to add manually.

Please provide me an alternative solution so that it should not disturb RTL files.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm pretty sure that's your only solution. There's no way to make your code reference something in another file without an actual reference. Or you could add the `ONE macro to this file, but if you don't want to edit the code, I'm not sure what you can do.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Below link mentioned, we can avoid `include <*.vh> But thats not working . Please check.

https://forums.intel.com/s/question/0D50P00004MgL0PSAV/is-there-a-way-to-include-file-with-macros-and-small-modules-without-having-to-use-include-in-every-file

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In the link provided, the code itself can pass compilation with and without 'include "macro.v" becuase it doesnt use the content defined in macro.v in the and_op.v.

The Intel Quartus Prime Pro Edition synthesis uses a different method to define the compilation unit. It follows the Single-file compilation unit (SFCU) method to select compilation unit files. In SFCU, each file is a compilation unit. Items visible only in the compilation-unit scope include macros, global declarations, and default net types. Therefore, you have to add `include in the main.v file.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You are right, in the image attached include file is not required but if you read the explanation below 2 lines are mentioned.

- We need to add the include (macro)files to the project and just compile for Quartus STD & LITE.

- For Quartus Pro, the compiler to search for macro file and include it during the compile process. No need to use `include in Verilog module. Please check the attached image

Similar to this I found one more query related to this

https://forums.intel.com/s/question/0D50P00003yyT6uSAE/unable-to-synthesize-the-design-with-macros-and-header-files-due-to-undefined-macros?language=en_US

please check on this.

It will be good if you can come back on solution as soon as possible.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

and also right in other compilers like synplify it doesn't expect `include.

SEARCH_PATH will able to resolve these type of issues. So, I felt there should be some solution in quartus.

Please review this as soon as possible.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may refer to the Intel Quartus Prime Pro Edition Getting Started User Guide (Chapter 5.4.1) https://www.intel.com/content/www/us/en/programmable/documentation/spj1513986956763.html#jbr1442966691310. This chapter states that

Items visible only in the compilation-unit scope include macros, global declarations, and default net types. The contents of included files become part of the compilation unit of the parent file. Modules, primitives, programs, interfaces, and packages are visible in all compilation units.

Therefore, you have to use 'include for macro.

Thanks.

Best regards

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

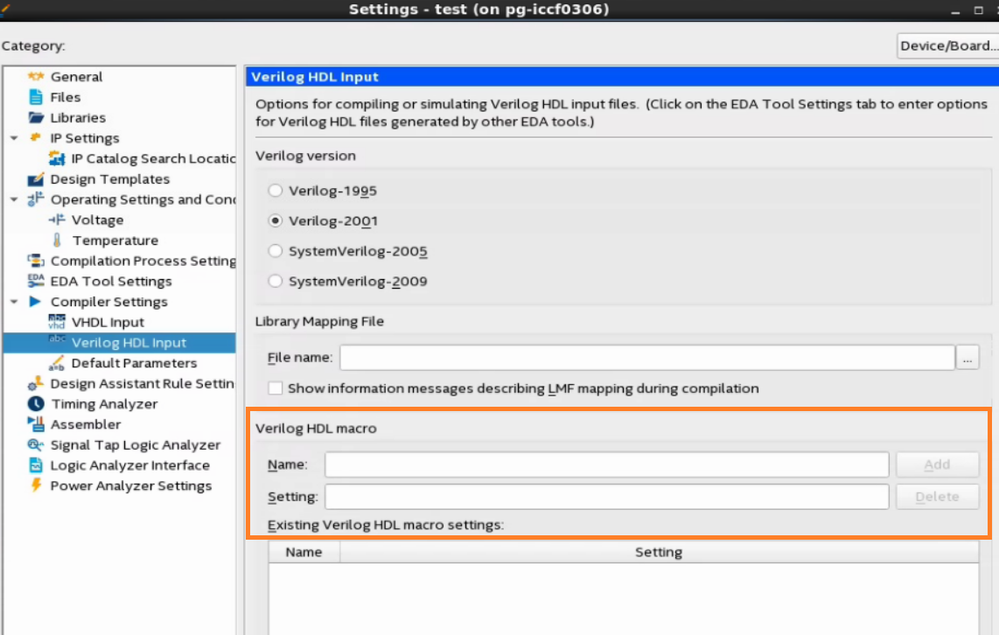

Upon checking with the team, you can define maco in the Compiler Settings by clicking on Assignments > Settings > Compiler Settings > Verilog HDL Input

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This is not my requirement.

My requirement is I need to add a include file to project instead of `define. In your solution I need to define Individual macros manually.

In my project there are lot of include files each contain lot macros so I can't declare each macro like that its a tedious process.

Regards

Sumukh B N

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have provided a suggestion to work around this offline. Please let me know if it doesnt work.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

After adding below statement this in my sample project qsf i created to reproduce the issue, I am not seeing the error.

set_global_assignment -name VERILOG_CU_MODE MFCU

Let me integrate it to my original project. Thanks for your support.

Regards

Sumukh B N

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page