- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

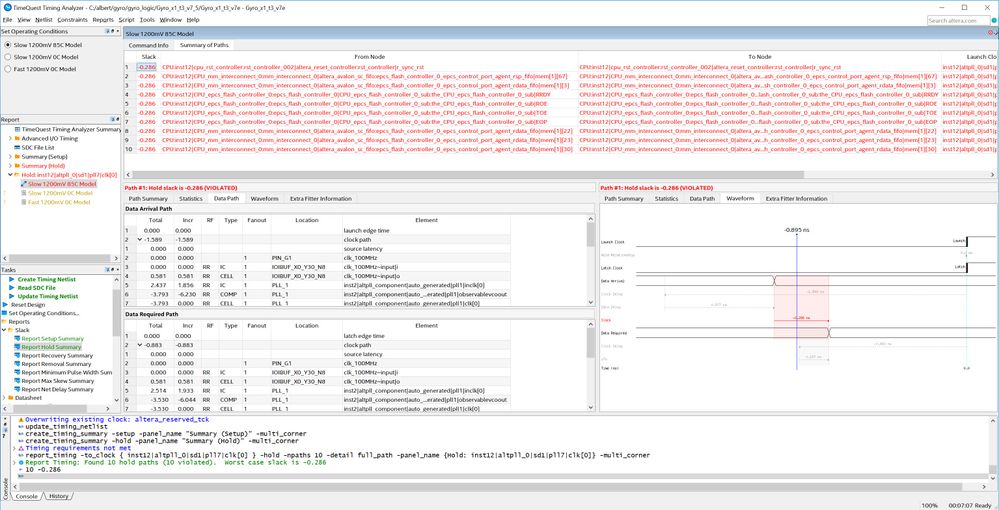

Most of the signals relate to NIOS. The design based on a single 100MHz clock. There is an additional clock 12.5MHz generated in pll in QSYS and connected only to epcs flash controller. I've seen similar connection of the epcs flash controller in some examples.

I get no setup time violations and functionally everything works fine. But I can't get rid of hold time violation warnings. See the attached TimeQuest Report. Please help.

Thank you.

Link Copied

- « Previous

-

- 1

- 2

- Next »

21 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Have you try the constraints? What is the result in the newer version?

Thanks.

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »