- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

From what i can tell the ADC module only needs a command to select which port to sample so how do i make pin assignments to confirm the ADC in use!

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hello there ,

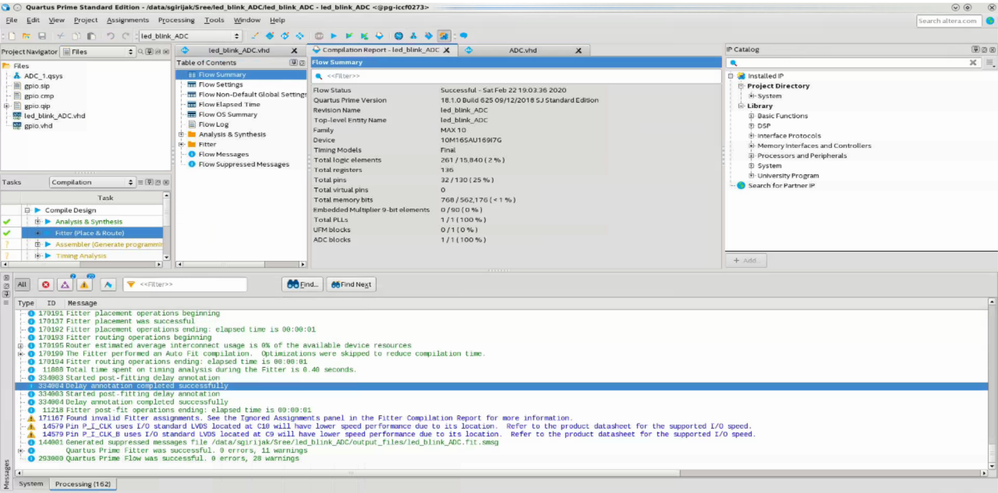

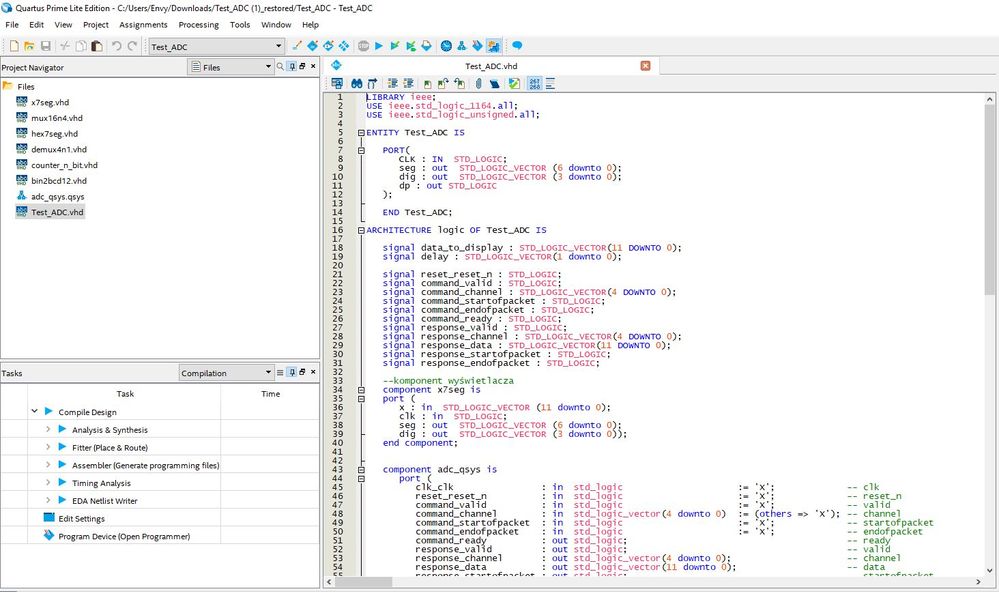

Here attached the screen shot and the modfied design file with ADC block utilization mentioned in the compliation report.

As of understood from the design you provided , quartus is optimizing the ADC block since it is no where used in the design.

In the modified design i instantiated the ADC input and clock as Input port which restrict the quartus to optimize the same.

Hope helps ,

Thank you ,

Regards,

Sree

링크가 복사됨

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

I am not following you , Hope you are using Max 10 right ?Can you kindly give more info for the same ? Would it possible to share the design ?

Thank you ,

Regards,

Sree

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

I'll try and re phrase the question- How do I assign the ADC1IN1-8 to ports on my top level design?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hello ,

I get chance to look your design , Looks part you selected is not support the ADC features. Only SA and DA parts supports the ADC. Here is the link for device overview for page 5 mentioned in the part number selection.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/m10_overview.pdf

when I open the IP in platform designer, i am getting error as mentioned "Error: max_ADC.modular_adc_0: The selected device part number 10M16SCU169I7G does not support ADC"

Can you use either SA or DA part to use the ADC feature ?

Thank you ,

Regards,

Sree

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

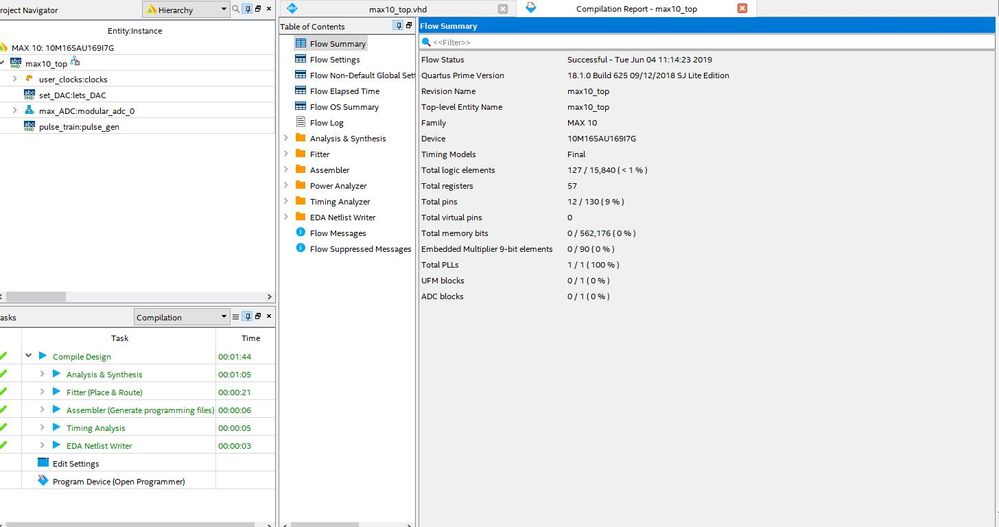

If you look at the above screenshot of the flow summary - it clearly shows a SAU device and also shows the no. of ADC blocks in the device but does not show it as used for the design even though the qsys file compiles!

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

But the design you send me as per below screen shot , with having error you wont be able to generate the HDL with error in qsys.

which one i should be believe your design files or your screen shot ? please clarify

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

I can confirm the right part number being used- SAU169I7G. If you use the right part number, can i see the flow summary on compilation and if depicts ADC block being used?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Here is the screen shot of compilation report attached.

One thing I noticed that you dont have a RTL for enable the channel or reading the ADC channels , I added a test logic directly enabled the channel "0" , Channel Valid and Channel start. After that I could see in ADC resources in compilation report. I think since the implemented RTL is not using ADC /enable the ADC Quartus is optimization is not instantiating the module.

Sorry , I dont know how to attach the file here ,Here is the added logic in the top module for your reference ,

command_channel <= "00000";

command_valid <= '1';

command_start <= '1';

command_ready <= '1';

process (P_I_CLK100,response_valid)

begin

if rising_edge(P_I_CLK100) and response_valid = '1' then

data_to_display <= response_data;

end if;

end process;

Thank you,

Regards,

Sree

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

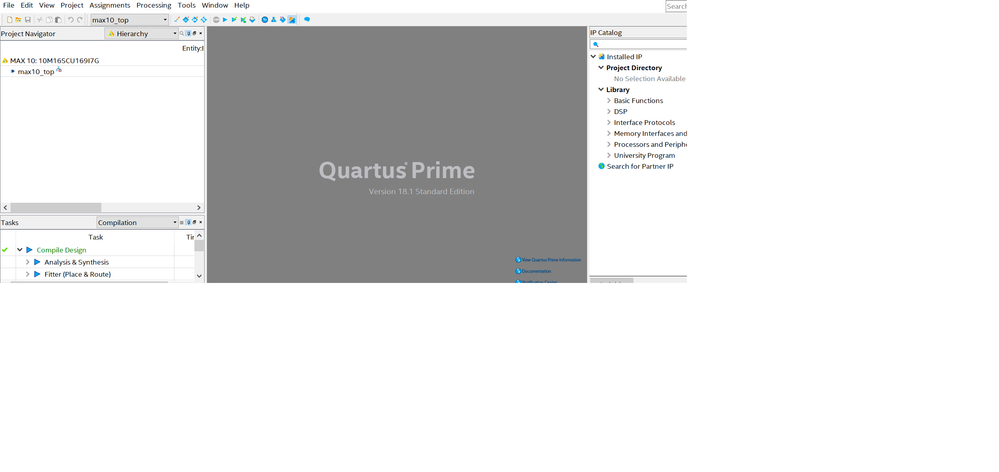

I added the above suggested logic but to no success. I even tried setting up a new project to double ensure the right part selection from the beginning, however I do not see the ADC module invoked neither the addition of the ADC pins in the final summary. Attached is the screenshot and top level module. I hope this is not a Quartus standard versus lite issue? And if the issue is not software related, can you send me the above depicted correctly compiled project+project files from your end?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

I added the above suggested logic but to no success. I even tried setting up a new project to double ensure the right part selection from the beginning, however I do not see the ADC module invoked neither the addition of the ADC pins in the final summary. Attached is the screenshot and top level module.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

I hope this is not a Quartus standard versus lite issue?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

And if the issue is not software related, can you send me the above depicted correctly compiled project+project files from your end?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

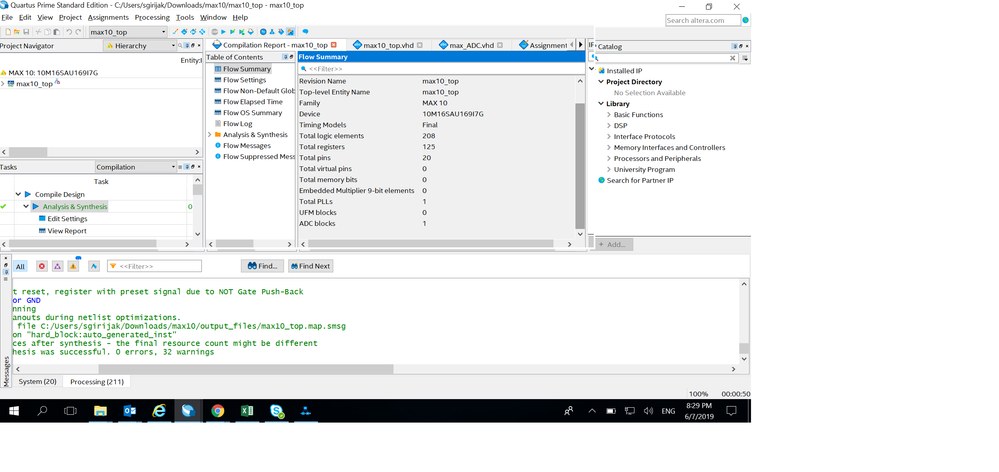

This is a project created by a blogger 'maximator' which once I edit to my design plans removes the ADC block for some reason. Can you send the project file specific to this query, please?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

I dont get you . I modified the project file which you sent to me . Please be clear what you really looking for . All the files related to the project file is already there in attachment.

Thanks ,

Regards,

Sree

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

That is not my project at all! Once I open it in quartus the following screenshot shows the different files similar tot the maximator project I mentioned. Can you please ensure the right project files?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

hmm..Can you attach your project file again (Full project .gar format)?

Thank you ,

Regards,

Sree