- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

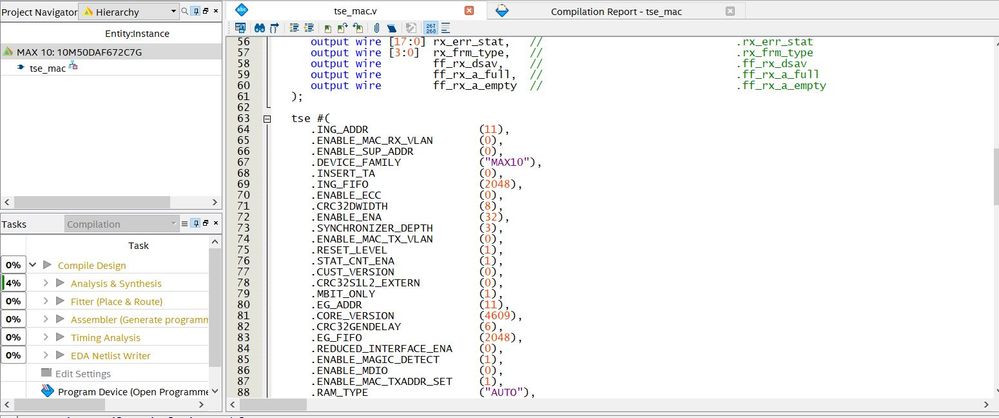

I have a Quartus project with a Platform Designer system where I have instantiated a Triple-Speed Ethernet Intel FPGA IP. However, I cannot compile a netlist without removing from Assignments-> Settings-> EDA Tool Settings the simulation option. In addition when I generate the automated script for Modelsim it cannot compile the simulation libraries for the IP. Is there a solution to simulate this module?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Let me add some info in order to be more precise. Quartus doesn't create the simulation library for the ethernet module. It doesn't exist in the simulation\modelsim\libraries folder like the rest of the simulation libraries for the other platform designer IPs. Therefore even though in the do file they are called to be compiled, they are not there.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know the bit more details?

- Quartus Edition(lite/pro/std) & version

- FPGA(Device) used

Refer "2.1.2. Generating a Design Example or Simulation Model" from the link below & try,

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_ethernet.pdf

-Thanks,

Vikas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have already done that but in the pdf it is clearly stated that "The dynamically generated design example for functional simulation is available only in Intel Arria 10, Intel Cyclone 10 GX, and Intel Stratix 10 devices. "

My project is for a Max 10 device. Does this mean that there are no simulation libraries for this module for a Max10?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

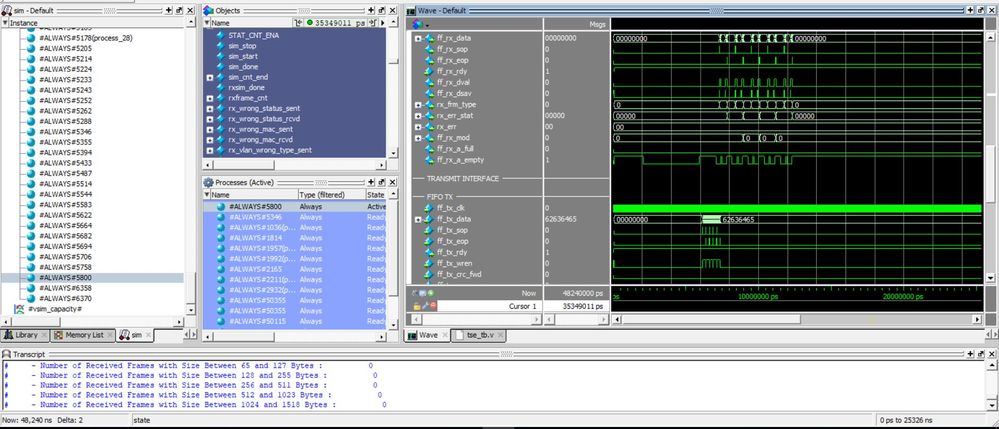

The errors I get in modelsim are the following:

# Loading i_tse_mac.altera_std_synchronizer_nocut

# ** Error (suppressible): (vsim-10000) <protected>(<protected>): Unresolved defparam reference to '<protected>'<protected>nofile.

# Time: 0 ps Iteration: 0 Protected: /tb_stamp3_top/inst_stamp3_top/inst_stamp3_platform_designer/eth_tse_0/i_tse_mac/genblk9/U_MAC_TOP/U_MAC/genblk2/U_RXFF/genblk3/RX_DATA/U_RAM File: nofile

# ** Error (suppressible): (vsim-10000) <protected>(<protected>): Unresolved defparam reference to '<protected>'<protected>nofile.

# Time: 0 ps Iteration: 0 Protected: /tb_stamp3_top/inst_stamp3_top/inst_stamp3_platform_designer/eth_tse_0/i_tse_mac/genblk9/U_MAC_TOP/U_MAC/genblk2/U_RXFF/genblk3/RX_DATA/U_RAM File: nofile

and others similar to these..

The problem is always the i_tse_mac library. It exists in the modelsim library list, I recompile the whole list, I used the tcl file generated in the .. platform_designer\eth_tse_0_testbench folder in modelsim and I still get the same error.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Do you have the license required for TSE MAC IP simulation &synthesis?

- When you generated the TSE MAC IP via Platform designer/Qsys, a window pops up asking if you want to generate the example design. Have you generated the example design?

- If not, then I suggest you re-generate the example design. This contains the simulation data for the IP. Two folders will be generated : <ip_name>_sim and <ip_name>_testbench.

- Navigate to the <ip_name>_testbench folder. Here you will find another QSF (Quartus project) that will generate the complete testbenches and sim data.

- Open the project named generate_sim.qsf in Quartus.

- From the tools menu select TCL Scripts..

- In the window that pops up, select the Generate testbench system (Verilog) and click Run. This will generate the complete testbench system with test cases for your IP that you have generated.

- Invoke ModelSim, change to the testbench_verilog folder, and then to the <ip_name> folder.

- Here you will find the following files :

- run_<ip_name>_tb.tcl

- <ip_name>_wave.do

- <ip_name>_tb.v

- Run the tcl file in ModelSim by issuing the following command : do <ip_name>_tb.tcl.

- This will start the simulation and you can see the outputs in the waveform viewer as well as in the console output window.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page