- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Some PLL clocks' loading is very light. So, I want to assign those PLL clocks to use the regional clock.

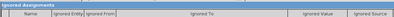

Unfortunately, the related regional clock assignments were ignored after compilation done as follows picture.

I don't directly want to use location assignment to assign a RCLK for PLL clocks.

I need Quartus tool to auto choose the best RCLK for PLL clocks.

How do I correct it? Could anyone help me to meet this? Thank you very much.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there

Can you check if you could use clock control block to achieve this?

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_altclock.pdf

thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi EngWei_O_Intel

Thank you, EngWei_O_Intel, very much. I will try it later. Could I just use assignment or other commands to meet it because the source code should be modified by RD?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If the assignments were ignored, chances are the Fitter was not able to find a placement solution for your clock network that would let it use the regional clock networks.

When you say your PLL clock loading is "light", what do you mean? Why do you think you need to do this? Are you not meeting timing/performance?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell

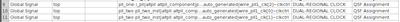

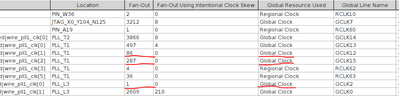

0.0, OK, I understand it that tool can't meet assignment. So, tool ignore it. And I said that PLL clock loading is "light" because fan-out are very less as follows picture.

My FPGA usage is to do SoC verification. So, I really want to assign those PLL clock to use regional clock because other clocks need to use global clock network to get better performance.

In critical cases, the design get a little timing violation, but it's OK because FPGA can work well in the normal environment.

Although FPGA can work well, I want to clear the timing violation to make sure the system is robust.

Does those ignored assignments are mean that if those PLL clocks use regional clocks, performance will get down?

Thank you, sstrell, very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No, not necessarily. It could mean that if those clock networks were used, the design would not be able to meet other requirements, such as meeting your timing requirements.

If you are seeing timing failures, you should investigate what those are related to and fix them.

Basically, if it ain't broke, don't fix it. If your design is working fine without using the dual regional clock, then there's no need to try to use them.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell

OK, I get it. Thank you, sstrell, very much.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page