- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am trying to implement the FFT block (with Quartus prime 19.1) but I cannot simulate it with simulink because I always get this error:

** Error: (vsim-3033) c:/intelfpga/17.1/quartus/bin64/db/ip/bloquefft/submodules/bloquefft_fft_ii_0.sv(59): Instantiation of 'asj_fft_si_se_so_bb' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /bloquefft_tb/bloquefft_inst/fft_ii_0 File: c:/intelfpga/17.1/quartus/bin64/db/ip/bloquefft/submodules/bloquefft_fft_ii_0.sv

# Searched libraries:

# C:/intelFPGA/17.1/modelsim_ase/altera/vhdl/altera

# C:/intelFPGA/17.1/modelsim_ase/altera/vhdl/220model

# C:/intelFPGA/17.1/modelsim_ase/altera/vhdl/sgate

# C:/intelFPGA/17.1/modelsim_ase/altera/vhdl/altera_mf

# C:/intelFPGA/17.1/modelsim_ase/altera/vhdl/altera_lnsim

# C:/intelFPGA/17.1/modelsim_ase/altera/vhdl/cyclonev

# C:/intelFPGA/17.1/quartus/bin64/simulation/modelsim/rtl_work

# C:/intelFPGA/17.1/quartus/bin64/simulation/modelsim/bloqueFFT

# C:/intelFPGA/17.1/quartus/bin64/simulation/modelsim/bloqueFFT

# ** Warning: (vsim-3473) Component instance "bloquefft_inst_clk_bfm : altera_avalon_clock_source" is not bound.

# Time: 0 ps Iteration: 0 Instance: /bloquefft_tb File: C:/intelFPGA/17.1/quartus/bin64/bloqueFFT/testbench/bloqueFFT_tb/simulation/bloqueFFT_tb.vhd

# ** Warning: (vsim-3473) Component instance "bloquefft_inst_rst_bfm : altera_avalon_reset_source" is not bound.

# Time: 0 ps Iteration: 0 Instance: /bloquefft_tb File: C:/intelFPGA/17.1/quartus/bin64/bloqueFFT/testbench/bloqueFFT_tb/simulation/bloqueFFT_tb.vhd

# ** Warning: (vsim-3473) Component instance "bloquefft_inst_sink_bfm : altera_conduit_bfm" is not bound.

# Time: 0 ps Iteration: 0 Instance: /bloquefft_tb File: C:/intelFPGA/17.1/quartus/bin64/bloqueFFT/testbench/bloqueFFT_tb/simulation/bloqueFFT_tb.vhd

# ** Warning: (vsim-3473) Component instance "bloquefft_inst_source_bfm : altera_conduit_bfm_0002" is not bound.

# Time: 0 ps Iteration: 0 Instance: /bloquefft_tb File: C:/intelFPGA/17.1/quartus/bin64/bloqueFFT/testbench/bloqueFFT_tb/simulation/bloqueFFT_tb.vhd

# Error loading design

# Error: Error loading design

# Pausing macro execution

# MACRO ./fft_on_top_run_msim_rtl_vhdl.do PAUSED at line 17

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, you have some inquiries related to simulating the FFT IP. Sorry for any confusion. Just would like to check if are trying to run simulation in Modelsim? If yes, for your information, you can try to run simulation with the example design using Modelsim Intel FPGA Edition. You may then refer to the example simulation and then cross check to see if you can spot any anomaly with your design.

You can try the following:

1. Open FFT IP

2. Go to Generate -> Generate Example Design

3. Open Modelsim and change directory to the fft_ii_0_example_design\simulation_scripts\mentor

4. source the msim_setup.tcl

5. type "ld" to run the compilation

6. Populate the waveforms and then type "run -all"

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, thank you for your answer.

I really want to generate a testbench to implement the inputs to the circuit myself because later I am going to add more blocks to the schematic.

I get the vsim 3033 error in modelsim when I generate testbench in the ip editor and do an rtl simulation with it.

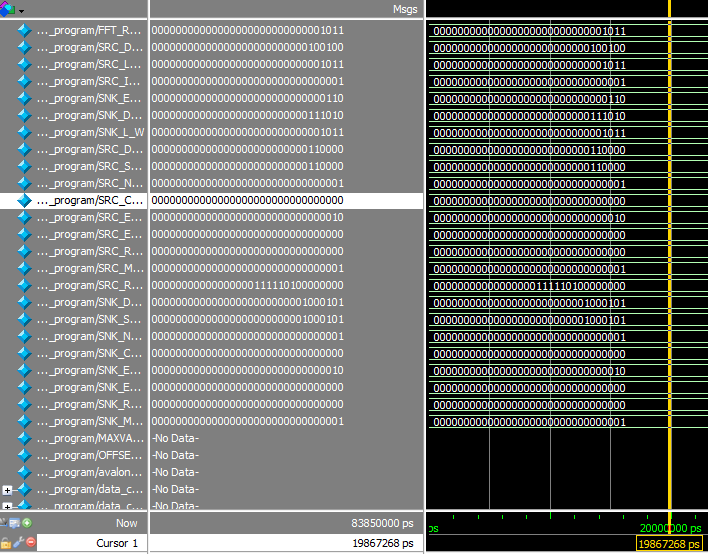

On the other hand, I have tried what you told me but I do not know how to handle modelsim very well and this is what I have obtained by following the steps.

Thank you for your time,

Best regards.

Ignacio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have emailed you a ZIP of the Q17.0 CV FFT IP generated design. You may do the following to simulate it:

- Unzip the files

- In Modelsim, change directory to the \simulation_scripts\mentor

- Type "source msim_setup.tcl"

- Type "ld"

- Type "do wave.do"

- Type "run -all"

- When message pops up asking if you want to finish the simulation, click "No"

You should be able to see the example simulation waveform. Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, thank you so much for your help.

I did it and it works.

But what I really want is to create a testbench for several blocks in the same schematic, specifically a filter that I will connect to the input of the fft ip.

I actually get the error when performing the rtl simulation after generating the testbench for the fft.

This is what I do:

1.Generate -> generate testbench system

2. start analysis and elaboration

3. RTL simulation

4. Error in modelsim v3033:

** Error: (vsim-3033) c: /intelfpga/17.1/quartus/bin64/db/ip/blockt/submodules/blocktff_fft_ii_0.sv (59): Instantiation of 'asj_fft_si_se_so_bb' failed. The design unit was not found.

...

# Error loading design

# Error: Error loading design

# Pausing macro execution

# MACRO ./fft_on_top_run_msim_rtl_vhdl.do PAUSED at line 17

It is the first time that I work with this program and it is possible that I am doing something wrong, but I found another person with the same problem and he solved it but with the Pro version. I cannot do the same because I am using the standard version.

https://forums.intel.com/s/question/0D50P00003yyO6LSAU/fft-ip-core-and-modelsim

Thank you for your time,

Ignacio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thanks for your update. Glad to hear that the IP generated example design is working. It means that no issue with your Modelsim simulator and built in libraries.

Based on your latest description, it is rather difficult to tell what might be wrong. But the following are some possible things that you can look into:

1. When you generate the HDL for the IP, remember to generate the simulation model as well.

2. By default, the msim_setup.tcl generated for an IP, is tailored to it. If you have multiple instances, then you will need to create a customized msim_setup.tcl which will compile all the instances in your design.

3. Following #2, you can use "Generate Simulator Script for IP" to generate a combined simulation script for all the instances in your design as workaround.

4. To ease the start, I would suggest that you start with simple one FFT instance in design, get pass the simulation. You can feed dummy data as start. Then slowly add more instance in simulation.

Hopefully these will be helpful.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Thank you for your reply.

I'm still stuck, I don't know how to fix the problem. These are the steps that I'm following to simulate the FFT Core, please tell me what I'm doing wrong:

1. Select device (Cyclone V GX starter kit)

2. New Schematic

3. FFT IP

3.1 Modify the features

3.2 Generate HDL

3.3 Generate-> Generate Testbench Model

4 Assignments-> Files-> Add All

5 Start Analysis and elaboration

6 Select generated Testbench in 3.3 (VHDL)

7 Simulation-> Run RTL Simulation

---ModelSim: error vsim 3033...

Best regards

Ignacio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. For your information, generally I will use standalone Modelsim to run simulation. As I tested running the test bench generated by the IP, it seems like it is only a framework example which required user to further customize it ie control the input and feed data into it. I would recommend you to try the following:

1. After generating the test bench from IP, you will need to customize it to control and feed data into the FFT instance

2. Open Modelsim, change directory to the \testbench\mentor

3. type "source msim_setup.tcl"

4. type "ld" to start compilation

5. Add your targeted signals into waveform

6. type "run -all" to start simulation

It is recommended for you to refer to the Example Design and code your own test bench. Alternatively, you can start customing from the Example Design.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much, I think it can work in that way.

The problem now is, that I don't know how to prepare the testbench to feed data to the block. Can you send me a manual or some instructions that I can follow to do it?

And the last question, the msim_setup.tcl is generated according to the testbench? If not, I don't see what the testbench affects in modelsim

Best regards,

Ignacio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. Regarding the test bench to feed data, there seems to be no specific manual or instruction on this. I would recommend you to refer to the example design generated from the IP which has the example test program which is reading data from text files to feed into the FFT IP.

Regarding the msim_setup.tcl generated together when you Generate Testbench, it is generated to compile libraries required for FFT simulation as well as the test bench generated. However, the test bench would require further edits ie to include the controls and the data feeding. I believe it is serving as a quick start for further edit.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page