Hello,

I have some basic questions:

My design includes a NIOS and an accelerator that is designed by myself. I designed a custom instruction to connect the accelerator and NIOS together. The custom instruction is connected to the accelerator by an Avalon Conduit interface.

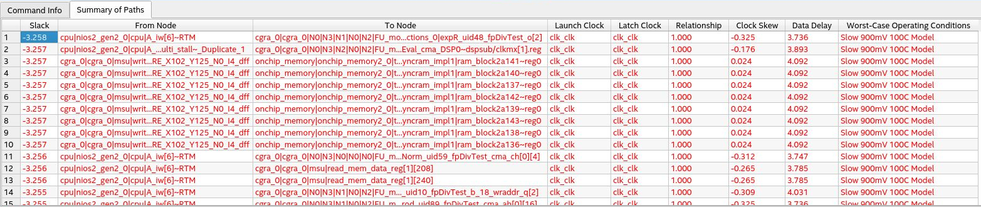

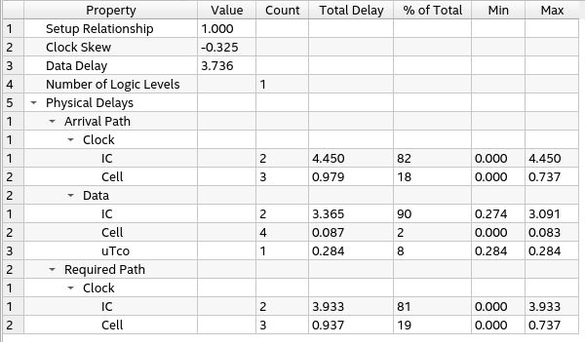

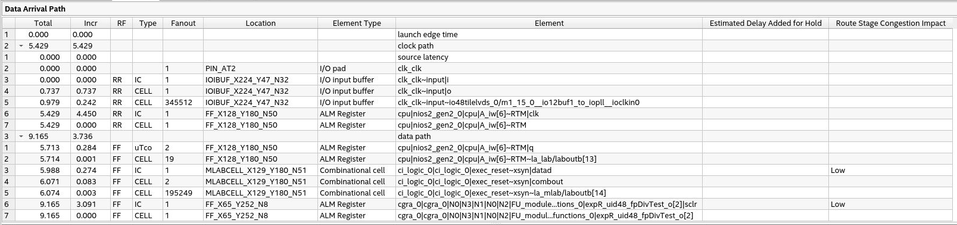

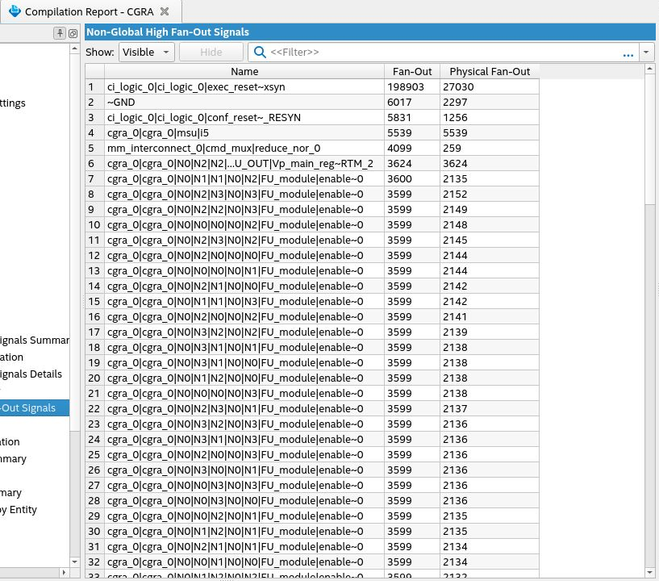

The problem is that the accelerator is too large and the conduit's signals need to go to all parts of this accelerator. As a result, Fmax is too low for my design, and I can see that most of the delay is related to interconnection delay.

My question is that how I can reduce this delay? Is putting FIFO between the custom instruction and the accelerator a good idea? In that case, is there any way to add this FIFO in the Platform Designer?

I have attached the delay for the most critical path, and also the routing utilization in Chip Planner including the most critical path.

Also, I would be thankful if I can get some useful documents about Timing Closure, and how to reduce the delay in Quartus.

Thanks

链接已复制

Hi,

You can refer here to get some ideas on how to improve the accelerator:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/nios2/edh_ed51006.pdf

Thank you for your answer. But, the main issue is the interconnection delay. That document basically gives you some ideas to have a better accelerator design.

I saw that there are only 2 logic levels which are not huge. The IC delay is likely due to the source and destination nodes being placed far away. As a start, are there a lot of fanouts from the source nodes or the combination logic? Or could there be some sort of nodes beyond this path that is pulling them in opposite direction (if you know what I mean)

Thanks for your reply.

Honestly, I am not sure how to find the answer to your questions. That's why I asked for some useful resources to learn about it. But anyway, I will be glad if you explain to me what is the problem based on the screenshots I attached to this message.

Please let me know if there is anything else to consider.

Thanks,

Mahdi

Hi,

It seems you are facing issue with the timing, you can refer below to learn on Timing Closure:

Hi,

Do you require further assistances?