- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

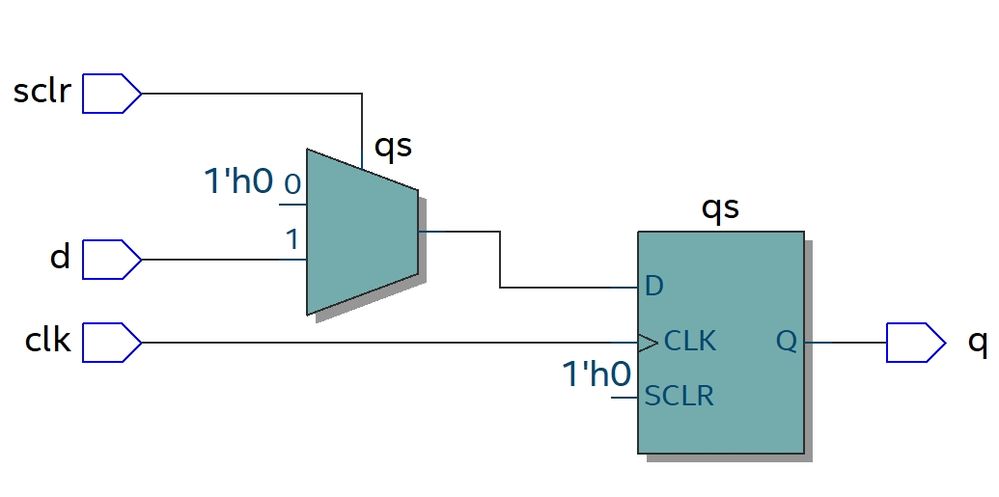

I am new in VHDL and the Quartus software. I was designing a simple flip flop circuit with synchronous clear by using sequential VHDL, but in the RTL schematic, it looks like it added a multiplexer to perform the synchronous clear task and didn't use the SCLR port of the flip flop. How can I add a synchronous clear without adding extra logic, please?

here is the code of the design and the RTL schematic.

library ieee;

use ieee.std_logic_1164.all;

entity ff_with_sclr is

port(d, clk, sclr: in std_logic;

q: out std_logic);

end ff_with_sclr;

architecture structure of ff_with_sclr is

signal qs: std_logic;

begin

process(clk)

begin

if (rising_edge(clk)) then

if(sclr = '0') then

qs <= '0';

else

qs <= d;

end if;

end if;

end process;

q <= qs;

end structure;Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

sclr is active high, so your if check should be if sclr = '1'. Also, there's no need for the extra qs signal. Just make the assignments to q in the process.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thank you for replying.

I changed the reset to be active high, but it still uses extra logic. the only difference is that the inputs of the multiplexers have flipped.

yes right, I too think there is no need for the qs signal here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can direct the tool to put the reset to SCLR pin by setting the synthesis setting Force Use of Synchronous Clear Signals=ON ( by default it is OFF).

Use below assignment:

set_global_assignment -name FORCE_SYNCH_CLEAR ON

FYI: By default, tool would turn off the option to use SCLR to because although the usage of SCLR helps to reduce the total number of logic cells used in the design, but it may negatively impact the fitting since synchronous control signals are shared by all the logic cells in a LAB.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page