- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Another question was open, it seems a duplicate but:

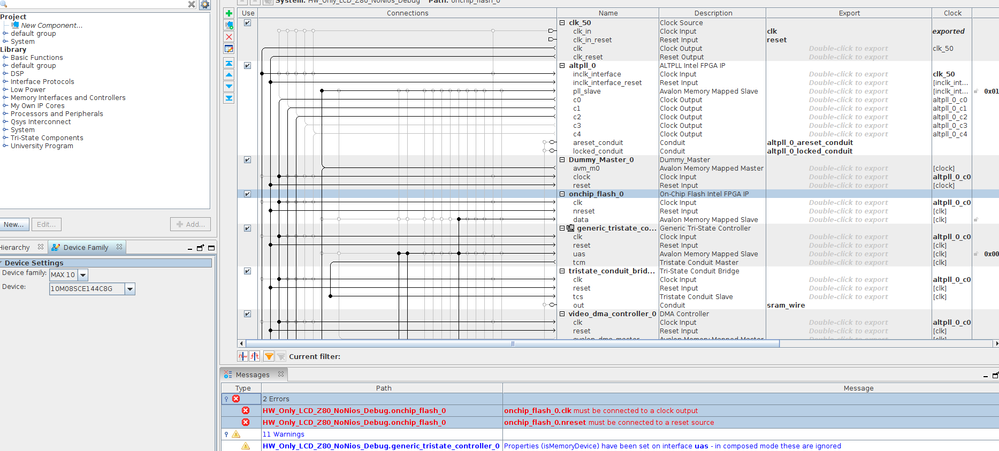

I restarted design of another board where exhibiting strange defect. Prepared a a fresh new project file, I reloaded all IP core and connected on QSYS, then I generated a ROM linked to HEX file, all seems good and project get the right way...

Correcting connection bug and parameter where mistyped,all seems good.

Relese another bug on forgot clock enable and LE usage grown from 2600LE to 5800LE .. init error return again and don' go away from!!

Don't go away removing files, removing rom and flash IP.

Don't go away cleaning project, rebuilding Qsys.

DOn't go away erasing ....

Cannot erase my job my time, reputation.

I start thinking quartus became a big crap, just try'd again oldest version and again same error.

Return to 18.1 clean project, no way to clean error.

QUARTUS is at this time unusable on MAX10, timing error reported on code it work, synthesis is wrong for sure.

Again Network module exhibit some strange issues, respond to ARP messages and do nothing other, at first compile probing from internal EThernet RX was dead.

Reversed RX and TX just to see if it where an hardware error on board, started working.

Appeared RX signal on internal route but It work? No reply just ARP.

To do so means it decode packet but after that?

Ip core was debugged and working.

Timing error where reported from internal PLL clock output?? How can I fix them?

Routed clock to external pin seems they where ok no jitter exact frequency....

LCD controller doesn't work properly. Image is stable but seems not initialized, I discovered processor was stopped...

Released no way to compile with rom in Qsys...

No way to recompile code, I think increased code consumed space, switched from sc08 to SC25, same scenario.

Removed rom, init files, still assembler refuse to compile.

New assembly has also new error on same code of previous project .

So I decided ask again google and I found this scaring thread:

https://forums.intel.com/s/question/0D50P00003yyRM5SAM/max10-flash-memory-specifications

Describe in exact word same pain I am suffering from when I started using MAX 10....

Datasheet are unclear and confusing and software tool is too much unreliable to use these device in a production. I have to suffer again to presentation, I feel the desire to change FPGA provider.

I got a low cost Lattice stick to do a test: code work as is.

I don' t own recent xilinx device, I provide an arrangement with fae on Monday to test my code on that platform.

Flow Status Assembler Failed - Fri May 24 16:36:07 2019

Quartus Prime Version 18.1.0 Build 625 09/12/2018 SJ Lite Edition

Revision Name Top

Top-level Entity Name top

Family MAX 10

Device 10M08SCE144C8G

Timing Models Final

Total logic elements 6,150 / 8,064 ( 76 % )

Total registers 2513

Total pins 95 / 101 ( 94 % )

Total virtual pins 0

Total memory bits 173,376 / 387,072 ( 45 % )

Embedded Multiplier 9-bit elements 0 / 48 ( 0 % )

Total PLLs 1 / 1 ( 100 % )

UFM blocks 1 / 1 ( 100 % )

ADC blocks 0

Error (14703): Invalid internal configuration mode for design with memory initialization

Error (14703): Invalid internal configuration mode for design with memory initialization

Error (14703): Invalid internal configuration mode for design with memory initialization

Error (14703): Invalid internal configuration mode for design with memory initialization

Error: Quartus Prime Assembler was unsuccessful. 16 errors, 1 warning

Error: Peak virtual memory: 840 megabytes

Error: Processing ended: Fri May 24 16:36:07 2019

Error: Elapsed time: 00:00:02

Error: Total CPU time (on all processors): 00:00:02

Error (293001): Quartus Prime Full Compilation was unsuccessful. 18 errors, 295 warnings

10M25SCE144C8G

Error (14703): Invalid internal configuration mode for design with memory initialization

Error (14703): Invalid internal configuration mode for design with memory initialization

Error (14703): Invalid internal configuration mode for design with memory initialization

Error: Quartus Prime Assembler was unsuccessful. 16 errors, 1 warning

Error: Peak virtual memory: 852 megabytes

Error: Processing ended: Fri May 24 16:29:23 2019

Error: Elapsed time: 00:00:02

Error: Total CPU time (on all processors): 00:00:03

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Lost another day...

Erasing rom from qsys seems not succesful

erased db, destination directory, all was not necessary.

Load Qsys file, rom is no more on fabric, erased.

On .qsysand .sopc file rom reference are still there and no way to remove by tools. It need editing XML by hand.

This again is a worst bug I fear can be related to same spreading issue on files.

The only way to remove error is to edif XML files with all related risk.

element onchip_memory_bios_rom_1

{

datum _sortIndex

{

value = "18";

type = "int";

}

}

element onchip_memory_bios_rom_1.s1

{

datum baseAddress

{

value = "65536";

type = "String";

}

}edit removing these lines.

again erase directory and .sopc file

open qsys

load cured .qsys files

need double save

generate

finish

on quartus

clear project

compile design

not enough what hell is there and where is hiding?

Restart from erasing directory, .sopc.

Edit again .qsys, inspect on details and remove every line has parameter related to rom.

Save , load on qsys, restart procedure and finally design compile again.

This is another annoying bug on QSYS, can be this related to PLL issue?

Flow Status Successful - Fri May 24 23:42:33 2019

Quartus Prime Version 18.1.0 Build 625 09/12/2018 SJ Lite Edition

Revision Name Top

Top-level Entity Name top

Family MAX 10

Device 10M08SCE144C8G

Timing Models Final

Total logic elements 5,553 / 8,064 ( 69 % )

Total registers 2151

Total pins 95 / 101 ( 94 % )

Total virtual pins 0

Total memory bits 33,476 / 387,072 ( 9 % )

Embedded Multiplier 9-bit elements 0 / 48 ( 0 % )

Total PLLs 1 / 1 ( 100 % )

UFM blocks 0 / 1 ( 0 % )

ADC blocks 0

So at almost figured how to get design again ready to build.

Understood rom is not usable as stated on forum link on previous post.

Now try with flash controller, this one may be usable and forever there. see Next post.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

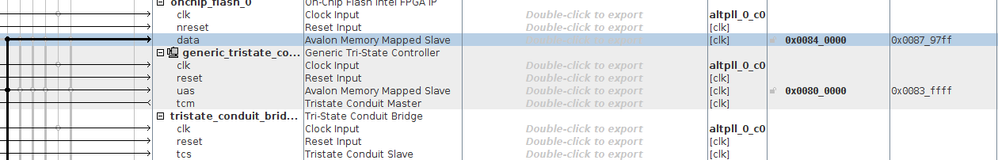

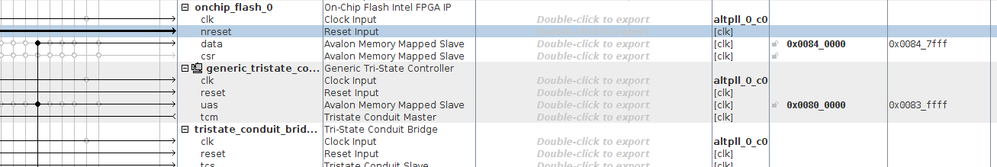

Now Flash controller test:

reenable has lost csr interface.

Qsys on reenable report clock and reset error, but they where on place:

double click on both clock and reset remove error.

Data has no address map, double click on data connection restore.

Save (forever twice) generate, then Quartus compile design to end. (not initialized flash.)

reopen qsys, delete Flash IP, select again from IP it is mapped where it was previous, again erase don't work. CSR reappear.

Flash is set as not initialized

Flow Status Successful - Sat May 25 00:11:17 2019

Quartus Prime Version 18.1.0 Build 625 09/12/2018 SJ Lite Edition

Revision Name Top

Top-level Entity Name top

Family MAX 10

Device 10M08SCE144C8G

Timing Models Final

Total logic elements 5,683 / 8,064 ( 70 % )

Total registers 2210

Total pins 95 / 101 ( 94 % )

Total virtual pins 0

Total memory bits 33,476 / 387,072 ( 9 % )

Embedded Multiplier 9-bit elements 0 / 48 ( 0 % )

Total PLLs 1 / 1 ( 100 % )

UFM blocks 1 / 1 ( 100 % )

ADC blocks 0

Reload Qsys, check initialize memory, point to bios for embedded processor, save and generate QSYS.

Quartus compile sa with uninitialized memory.

Browsing .pof and .sof with an HEX viewer no trace of bios is seen on files.

Try with convert programming files...

MAX 10 can be an Heaven to embedded SOC, turn on Hell by software and lack of documentation....

Edit UPDATE:

modified configuration of flash to initialized, added .hex bios files, everything proceeded fine.

Flash content where is stored on .pof? or .sof? I don't see bios ascii messages, nor I see code, just a long FF sequence and some spot of noise, can be cfm

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

About Flash content:

File reside on .pof, is forever scrambled same way, maybe it add some check bit.

Strange scrambling of file was from QSYS, sometimes when forget double save generate code on old design.

If this happen and some IP core got modified, next time on qsys opening ask update Cores.

After that I seen clock was moved from PLL C0 output to main clock.

Correcting this, now flash content on read is stable and close to .hex.

Too many sparse subtle bug affect this tools.

Old bug never addressed still persist on. (Double save)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If you want to store in internal flash or want to load image after power cycle, you can use pof file.

If you just want program fpga, used sof file (your image will missing after power cycle).

For your design above, I think stored your image on .pof file.

Thanks😉

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi MShafiq, good answer!

No compilation no pof nor sof!

CANNOT GET DESIGN COMPILED, so no ram initialization, more than one bug is report there.

These annoying bug and Altera/Now Intel answer are very upsetting.

Reread and you find all about this multiple bug on memory initialization.

some test changing content of hex memory file revealed UFM image is just on .pof, .sof does'nt change.

No idea about IPcore ram rom, cannot get design compiled.

When i try read UFM i read garbage then some sequence of hex file but with odd offset I cannot figure where it come from.

I try'd too many test, MAX10 was great, now is scrap due to bad software and support too.

Using "convert programming file" combining both .sof and .hex file produce a .pof identical to design output.

Best regards.

Roberto

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page