- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

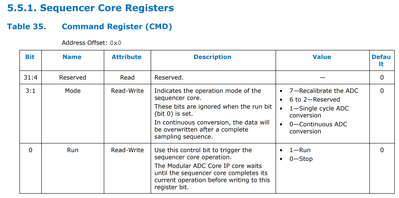

Hi, I configured the ADC of the MAX10 on Quartus, I powered it but I am stuck in the initialization of this last one, I wrote a code to initialize it but I still cannot have the data. It's in sample_store_csr_readdata where there are the samples, I put the address to 0x0000000 and the read to 1 and to initialize the ADC I put the address to 0x0, write to 1 and writedata to 1 because bit 0 corresponds to the initialization of the ADC.

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi MAYLIS,

I have difficulty understanding the term 'initialization'. To initialize means bit 0 of CMD register = '1' i.e. Run?

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_adc.pdf

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello !!

Thanks for your reply. Exactly, to run it, I have to set bit 0 to 1, I am attaching a screenshot of the datasheet.

Here is my code for the initialization, I put also the sample_read to 1 so that I can activate data reading that I will recover them then with a PIO, but I still don't succeed I don't know the error it comes from where :

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for sharing the code.

The problem is that there is no handshake mechanism between data_initialisation entity and the ADC IP.

Once you give a Run command, you need to wait for the sample_store_irq_irq signal from the IP to indicate that the digital data is ready to be read.

Then you should initiate a read command to the sample store csr interface to get that digital data.

After initiating the read expect the data at the next clock edge from when the csr interface gets the read command. This is due to Avalon-MM interface latency.

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

There are some videos available on Intel FPGA YouTube channel. Providing link for one of them for your reference.

https://www.youtube.com/watch?v=6UscboZ1Vho

Regards.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page