- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sir/Madam,

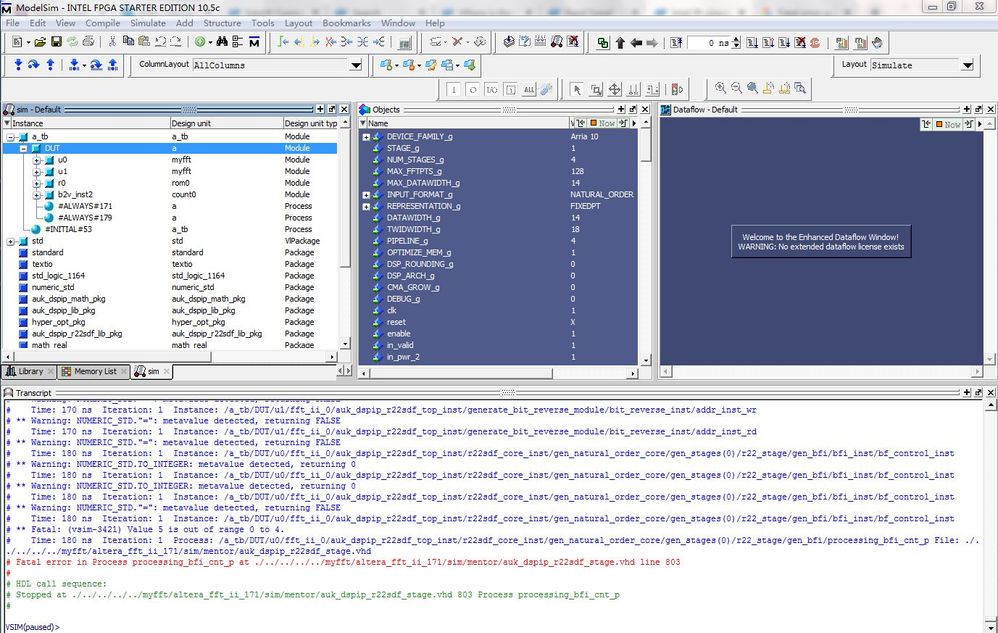

Basic Information Quartus prime pro 17.1 + Modelsim-Intel Starter edition 10.5c +Arria10gx

I generated an Intel FFT ip core, because option to generate a design example is in grey color and not available to choose on IP platform designer.

,so I have make my own one, I have installed 1 fft and ifft into my top level design. Acturally ,I was trying to duplicate the example I downloaded from Intel forum, but example uses different version and different device .

Because design also has rom and counter unit, so I have to to manually compile them into work library in modelsim.

1,source tcl msim_setup.tcl

2, ld

3, manually add top level signals of testbench into waves window

4,run –a

5,check the waveform, I can see the many signals are working as I expected, but suddenly stop in below stage

The error part is not my design, and it seems the low level library being called by upper design, I have no idea how to to fix them.

I have close the modelsim, restart ,computer and simulated it again, got exactly same result as before.

# ** Warning: NUMERIC_STD."=": metavalue detected, returning FALSE

# Time: 180 ns Iteration: 1 Instance: /a_tb/DUT/u0/fft_ii_0/auk_dspip_r22sdf_top_inst/r22sdf_core_inst/gen_natural_order_core/gen_stages(0)/r22_stage/gen_bfi/bfi_inst/bf_control_inst

# ** Fatal: (vsim-3421) Value 5 is out of range 0 to 4.

# Time: 180 ns Iteration: 1 Process: /a_tb/DUT/u0/fft_ii_0/auk_dspip_r22sdf_top_inst/r22sdf_core_inst/gen_natural_order_core/gen_stages(0)/r22_stage/gen_bfi/processing_bfi_cnt_p File: ./../../../../myfft/altera_fft_ii_171/sim/mentor/auk_dspip_r22sdf_stage.vhd

# Fatal error in Process processing_bfi_cnt_p at ./../../../../myfft/altera_fft_ii_171/sim/mentor/auk_dspip_r22sdf_stage.vhd line 803

Any suggestion is welcome

Jim

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jim,

My first debug step would be, go to auk_dspip_r22sdf_stage.vhd line 803, figure out which variable is implicated and adjust its declaration range. This may fix the problem or cause another. But it might give you a clue.

Thanks,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Did you ever find a solution to this problem? I am running into the same error.

Here is a description of the problem:

- The simulation runs initially but stops with a fatal error once the FFT begins sourcing samples

# ** Fatal: (vsim-3421) Value -1 is out of range 0 to 4.

# Time: 21980 ps Iteration: 1 Process: /ifft_tb/u0/auk_dspip_r22sdf_top_inst/r22sdf_core_inst/gen_natural_order_core/gen_stages(0)/r22_stage/gen_bfi/processing_bfi_cnt_p File: ./ifft_ip/simulation/submodules/mentor/auk_dspip_r22sdf_stage.vhd Line: 789

# Fatal error in Process processing_bfi_cnt_p at ./ifft_ip/simulation/submodules/mentor/auk_dspip_r22sdf_stage.vhd line 789 - From the beginning of the simulation, I get many warnings like this

Warning: NUMERIC_STD."=": metavalue detected, returning FALSE

# Time: 2500 ps Iteration: 1 Instance: /ifft_tb/u0/auk_dspip_r22sdf_top_inst/r22sdf_core_inst/gen_natural_order_core/gen_stages(0)/r22_stage/gen_bfii/bfii_inst/bf_control_inst

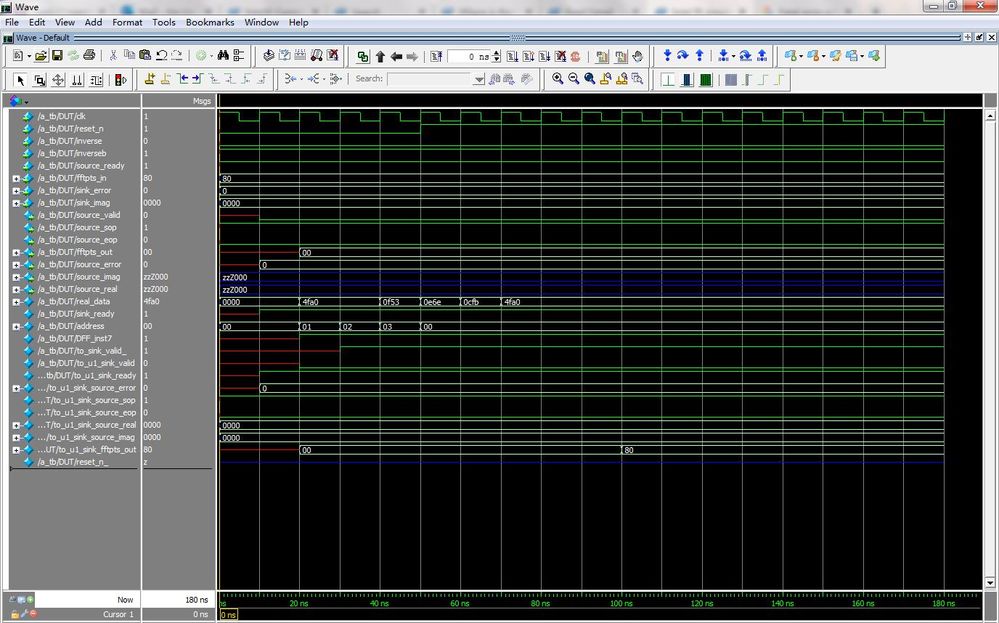

I see in the waveform viewer that several signals in gen_natural_order_core/gen_stages(0)/r22_stage have undefined values: bfi_out_real, bfi_out_img, and twidaddr_s

So perhaps there's something wrong in generating the correct twiddle address? Or with generating the natural bit order?

I've generated theFFT IP core with the following parameters:

- Variable streaming

- Length = 128

- Natural Input Order

- Natural Output Order

- Direction = Bidirectional

- Fixed Point representation

- Data Input Width = 16 bits

- Twiddle Width = 32 bits

- Data Output Width = 16 bits

I am using:

- ModelSim Starter Edition 2020.1

- Quartus Prime Version 20.1.1 Build 720 11/11/2020 SJ Lite Edition

After generating the HDL, I created a TCL file "mentor.do" based on the template "msim_setup.tcl" (both attached).

I am running a simple testbench "ifft_tb.sv" (attached).

Thanks for any insight!

Thanks,

PBJ

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I make it short before I write a lot of stuff... Ready to discuss this though if somebody replies.

I do run into the same problem with Quartus 18.1.

Is there any solution for this?

Thanks,

Maik

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We sincerely apologize for the inconvenience caused by the delay in addressing your Forum queries. Due to an unexpected back-end issue in our system, your Forum case, did not reach us as intended. As a result, we have a backlog of cases that we are currently working through.

Please be assured that we are doing everything we can to resolve this as quickly as possible. This will take some time, and we appreciate your patience and understanding during this period of time. Your case will be attended by AE soonest possible.

Thank you again for your patience and understanding, and we are committed to provide you with the best possible support.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page