- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

I m Newbie

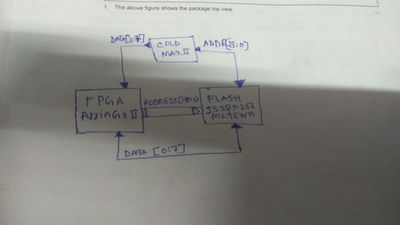

I am trying to configure EP2AGX Arria® II GX using EPM240 Max ii CPLD and on board CFI Flash js28f256m29ewh using PFL IP.

In my case our custom Board flash Address bus 24bit bus and Data 8bit Bus from FPGA conected as per PFL requirement

but in case of CPLD only connected with 24bit Addresses to Flash and Data bus is not contected between CPLD and CFI Flash

below picture as shown

my question is

1.how configure PFL for CFI flash program from CPLD ?

2.can i program by using PFL from FPGA ?

What will the best option for me please help us.

Nome

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for contacting Intel community.

We would recommend you to refer to Intel FPGA PFL userguide below:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_pfl.pdf

Let us know if you have any concern.

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Sir

Thanks for your reply

In my case I wrote my above post our custom board doesn't have directly CPLD to CFI data port there

thats why I am confused how to define PFL_flash_data [0] to PFL_flash_data[7] in PFL? CFI flash D15 also connected with CPLD.

PFL_flash_addr[0] to PFL_flash_addr[24] CPLD to CFI connected there

all require another pin connected between CPLD and CFI Flash like nce,we,oe etc

Thanks

Nome

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i have found 10 more pins between cpld and fpga

i am totally confused

how configure PFL

as in ug_pfl. pdf i couldn't find out how configure if we don't have data bus between cfi and cpld

please help me

thank

nome

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nome,

No connection is needed between Arria II and flash, this is because it will be control by PFL and CPLD(Max 10) to load in Arria II.

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your reply

sir i am not talking about connection between Arria fpga and flash.

I am talking about data bus between cpld max II and flash

if we doesn't have physically data bus between Max II and flash how pfl will work?

Thanks

nome

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

I m new in parallel Flashing

I want to know Regarding NIOS processor Flashing How to make Boot by using PFL?

what will Roll of CPLD?

How to Flashing Boot Area after it will able to using NIOS Flashing

I am totally confused

Our hardware is Arria II GX and and CPLD MAX II js28f256m29ewh Flash

Thanks

Nome

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page