- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

in Quartus I get following warning message (same message for PLL_FRT and PLL_ADC_intern):

Warning: PLL "PLL_FRT:PLL_FRT_inst|PLL_FRT_altpll_0:altpll_0|PLL_FRT_altpll_0_altpll_nr22:sd1|pll7" input clock inclk[0] is not fully compensated and may have reduced jitter performance because it is fed by a non-dedicated input

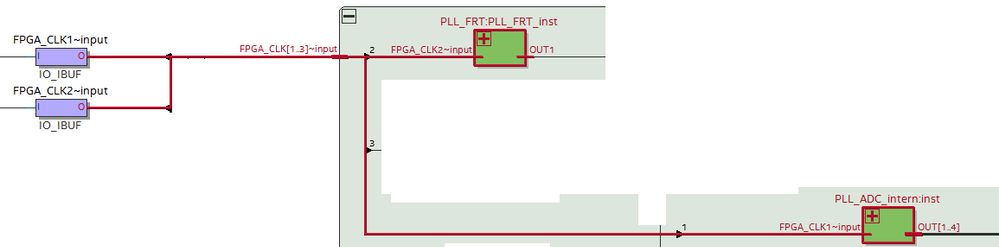

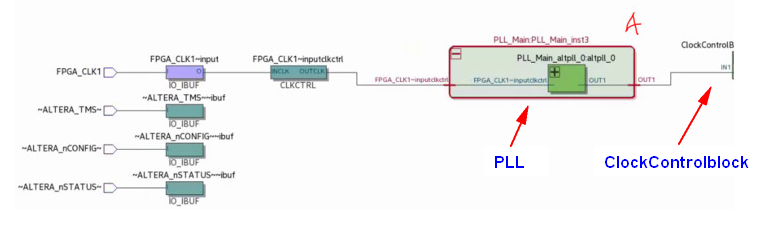

The PLL itself is fed from the clock input pin which is a dedicated clock pin according the pin planner (CLK0p). This clock pin is only used once for each PLL as shown below (red line):

Question:

- What exactly means this warning message if the PLL clock comes directly from the input clock pin?

- How to solve this warning messages?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You don't mention the device, but you may be using the wrong dedicated clock input pin for this particular PLL. Check your device handbook to see which is the correct pin to use for a particular PLL.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Norick,

Which quartus version?

Which device? PN needed.

Which pin?

It would be great if you can attached a simple design that shows the problem here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using:

- Quartus: 18.0.0 Build 614 Lite Edition

- Max10 10M40DAF256I7G

The used pins of the Max10 are:

- FPGA_CLK1 --> Max10 Pin_K6

- FPGA_CLK2 --> Max10 Pin_J11

The design is shown above. At the moment there is NO special assignement done in order set a specific PLL to a specifif clock source!

Question:

- Do I need to assign a specific PLL to my clock input? If yes, how can I do it?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Norick

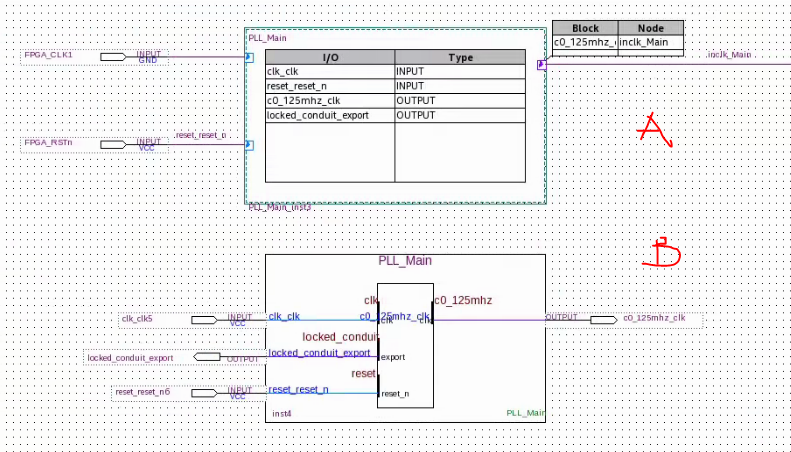

I created a simple design based on your description (attached). It all compiled correctly. Im using Standard Edition, though.

At the least, you can compare the difference. If possible, test with Standard Edition.

As for your question:

- Do I need to assign a specific PLL to my clock input? If yes, how can I do it?

Ans: No, you dont have to specify the PLL. Based on your RTL connection, fitter will know the input pin is routed to which PLL.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello JwChin

thanks for the answer and the test-project. The problem I am dealing with, is that I get following warning message:

Warning: PLL "PLL_FRT:PLL_FRT_inst|PLL_FRT_altpll_0:altpll_0|PLL_FRT_altpll_0_altpll_nr22:sd1|pll7" input clock inclk[0] is not fully compensated and may have reduced jitter performance because it is fed by a non-dedicated input

The question here is:

- why I get this warning and how can I eliminate it?

- What is the meaning of "non-dedicated input" for my PLL if the fitter selects the right PLL?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Norick

May i know did you see the warning using earlier attached design?

Or better, if you can provide me a simple design that shows the error, i can confirm it on my end.

Normally, you will see this warning when you use normal IO instead of dedicated clock pin.

Im not sure why you are seeing those errors if you are already using dedicated pins. I hope you can test the design, and let me know the results. Then only i can help further.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

attached I send you a simple design with following warning messages:

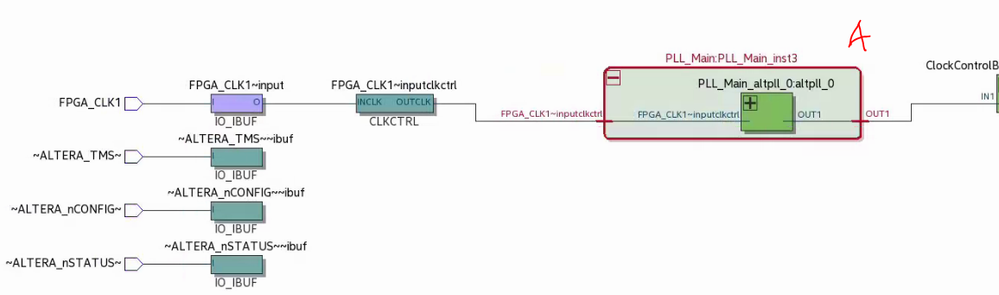

Warning (15055): PLL "PLL_Main:PLL_Main_inst3|PLL_Main_altpll_0:altpll_0|PLL_Main_altpll_0_altpll_hl92:sd1|pll7" input clock inclk[0] is not fully compensated and may have reduced jitter performance because it is fed by a non-dedicated input

Info (15024): Input port INCLK[0] of node "PLL_Main:PLL_Main_inst3|PLL_Main_altpll_0:altpll_0|PLL_Main_altpll_0_altpll_hl92:sd1|pll7" is driven by FPGA_CLK1~inputclkctrl which is OUTCLK output port of Clock control block type node FPGA_CLK1~inputclkctrl

Warning (15058): PLL "PLL_Main:PLL_Main_inst3|PLL_Main_altpll_0:altpll_0|PLL_Main_altpll_0_altpll_hl92:sd1|pll7" is in normal or source synchronous mode with output clock "compensate_clock" set to clk[0] that is not fully compensated because it feeds an output pin -- only PLLs in zero delay buffer mode can fully compensate output pins

Warning (15064): PLL "PLL_Main:PLL_Main_inst3|PLL_Main_altpll_0:altpll_0|PLL_Main_altpll_0_altpll_hl92:sd1|pll7" output port clk[0] feeds output pin "clk~output" via non-dedicated routing -- jitter performance depends on switching rate of other design elements. Use PLL dedicated clock outputs to ensure jitter performance

Question:

- Why do I get those warnings?

- How to eliminate those warnings?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Norick

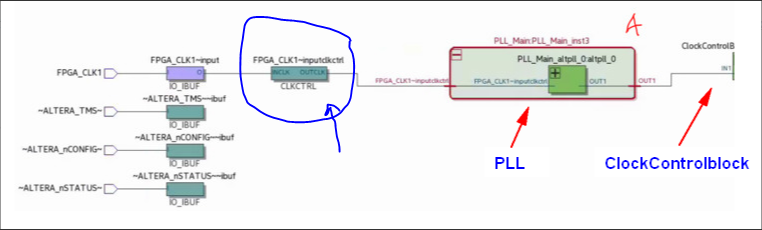

A is the block symbol you created. I can see the same error as you mentioned.

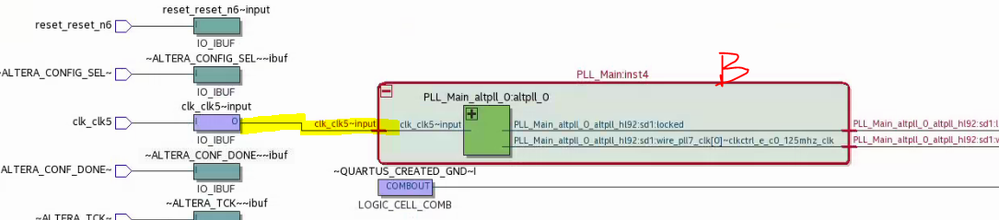

B is the bsf symbol i created from your qsys file. B works fine on my end.

I am not sure how you created BlockA, but that seems to put a clkctrl block in between your input pin and pll. Thus the warning message.

In BlockB, you can see that the clock pin is connected directly to the PLL. You wont see the warning message.

I attached the QAR which BlockB is created in pllgenjwtop.bdf (as top file).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

well I do not see any difference between A and B as you mentioned (see yellow marking in B). The only difference is that you are using clk5 - that's all. On the other side you changed the origin design and cut off the clock control block (see orign file at the top again). Of course without clock control block the warning dissapear but again it is a different design.

Therefore I am still confused about the warning message... could you please use my posted design and change it in order to get rid of the warning message? Therefore we have the same design from scratch and a solution would be clear.

The PLL Block (see A) is the same as your B. The difference is that I insert it in the scheme as "Insert symbol as block".

thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Norick

On the other side you changed the origin design and cut off the clock control block (see orign file at the top again). Of course without clock control block the warning dissapear but again it is a different design.

==> Yes, that's what im trying to say. It is the clock control block that is causing the problem. Thus, my recommendation is to instantiate as "B" (not A), you shouldnt have a CLKCTRL block in between. The CLKCTRL routes to a clock network, e.g. GCLK before going to the PLL. Thus the warning.

If you want to avoid the warning, connect the dedicated input clk pin directly to PLL (without CLKCTRL in between).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello JwChin

you say "connect the dedicated input clk pin directly to PLL (without CLKCTRL in between)" but in my design I have the PLL followed by the clock controlblock.

The idea is to power down the clock network after the PLL in order to minimize the power consumption. How would you do this?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Norick

I am referring to the CLKCTRL before the PLL. See screenshot.

Maybe is the way you instantiate your block that puts the CLKCTRL there.

As for the ClockControlblock after the PLL, that is not related to the warning.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello JwChin

now, I think I understand the problem here. First of all the diagram you showed is the Post Fitting Map Viewer. This is quite importand because the other viewers does not show this contolblock at all!

Second, the showed controlblock is not part of my design and therefore I focused on the assignment editor. Here I have seen that the FPGA_CLK1 has been set as "global signal" and was enabled. Therefore

Quartus put in such controlblock before the PLL!

After disabling it the warning messages is gone and everything fine :)

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Being totally new to Altera I Used the Mega Wizard to create my PLL, however I cant see a setting that turns off the clkctrl buffer. Can anybody advise me as to how to do this in Quartus II V11 please?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page