- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Since we have provided the workaround, and we do not receive any response from you to the previous answer that we have provided. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

Enlace copiado

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Seems like I cannot duplicate this from my side, can you attached your design.qar files to have a look? You can look into your email to attached a file.

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Also, you may need to let us know what OS that you were using?

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Thanks for attaching the design,

Look into the content of *.qip in Q20.1, it seems that it is still using Altera FP function.

If you open up the IP catalog, you will notice that the name change from Altera to Intel.

Which means, you cannot do direct migration on this,

Can you do the following:

1) recreate the FP_function_intel_fpga in the ip catalog for 20.1.

2) follow the setting that you have in 18.0

See if you still hit the error in windows 10?

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

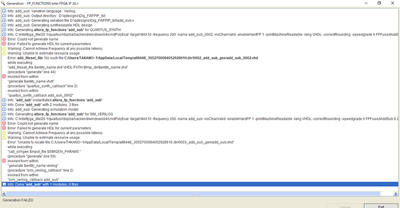

20.1のFP_FUNCTIONS Intel FPGA IPについて確認、指示をいただきまして、ありがとうございます。

作成したFPIP_tstプロジェクトのqipファイルの内容を確認しますと、

IP_TOOL_VERSION "20.1"にもかかわらず、IP_TOOL_NAME "altera_fp_functions"になっていることを

確認しました。

そこで、Project Navigator欄の"add_sub.qip"を一旦削除し、FP_FUNCTIONS Intel FPGA IPで"add_sub.v"

を再作成するのですが、Generation Faildが発生します。

又、Project Navigator欄の"add_sub.qip"項目にadd_sub_0002が登録されていなくて、

Analysis & Elaborationを実行した時に下記のエラーメッセージが発生しています。

Error (12006): Node instance "add_sub_inst" instantiates undefined entity "add_sub_0002". Ensure that required library paths are specified correctly, define the specified entity, or change the instantiation. If this entity represents Intel FPGA or third-party IP, generate the synthesis files for the IP.

Error: Quartus Prime Analysis & Elaboration was unsuccessful. 1 error, 1 warning

Error: Peak virtual memory: 4804 megabytes

Error: Processing ended: Fri Jul 10 08:16:06 2020

Error: Elapsed time: 00:00:15

Error: Total CPU time (on all processors): 00:00:30

どのように対処すればよいか、ご教示お願いいたします。

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Can you reattached your modified design? You may send the design in email.

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

I cannot find the files in the mail, can you reattached it?

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Thanks for your attachment,

To work around this problem, Can you try to generate the add_sub Intel FPGA IP in Quartus® Prime std Edition software version 18.0 and use the RTL generated files to Quartus Prime std Edition software version 20.1?

I test the workaround above on my side, it seems to work. I will log a bug to our developer to fix it.

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Since we have provided the workaround, and we do not receive any response from you to the previous answer that we have provided. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

- Suscribirse a un feed RSS

- Marcar tema como nuevo

- Marcar tema como leído

- Flotar este Tema para el usuario actual

- Favorito

- Suscribir

- Página de impresión sencilla