- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

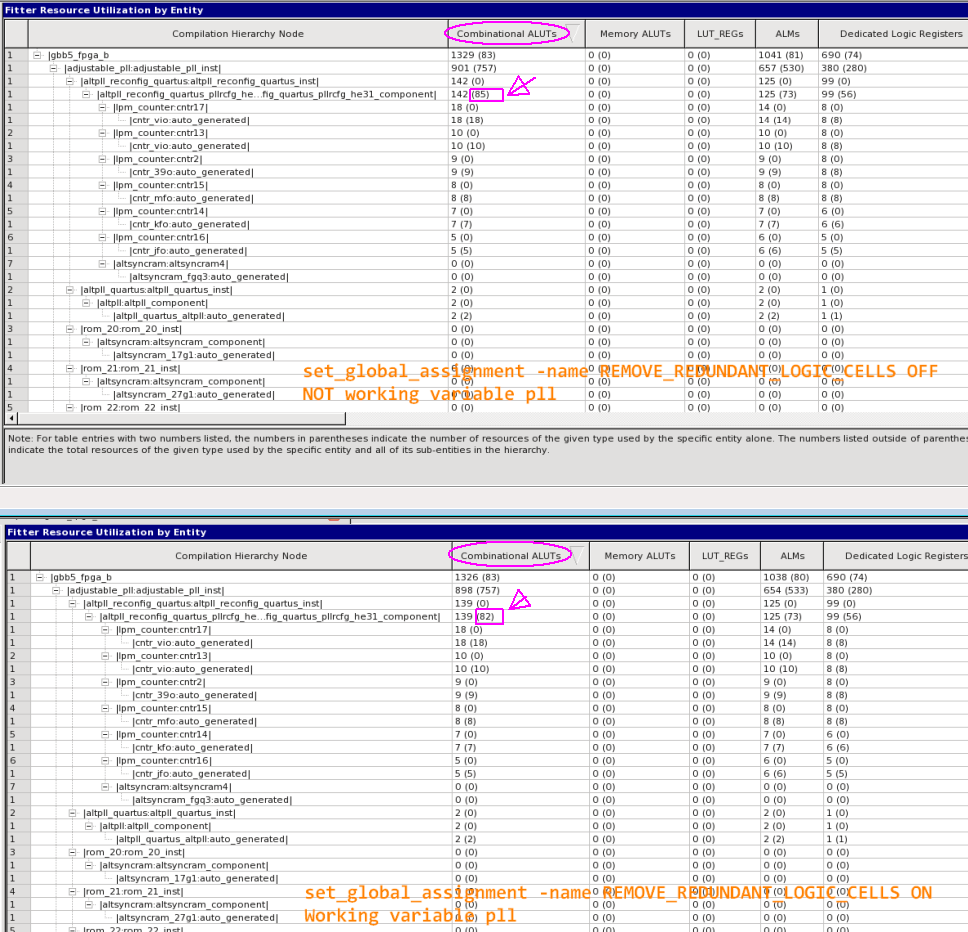

Pay attention to leave the REMOVE_REDUNDANT_LOGIC_CELLS option to ON if you are using a reconfig pll [at least in stratix 3 FPGA].

Turning the option OFF makes 3 redundant cells not removed and the PLL fails to produce aproper clock after reconfiguration.

File is altpll_reconfig_quartus.vhd,

SIGNAL cuda_combout_wire : STD_LOGIC_VECTOR (3 DOWNTO 0);

--Quartus VERSION 13.1

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you circle out the different base on your screenshot?

I will try it on Q18.1 to see if the problem still exist.

Thanks,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please see the diff in the new attachment.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please note that timings are meet for setup and hold in both scenario's,

so this is not timing related (slack of +0.3 ns).

If you need the qar to reproduce it, let me know (give me your personal placeholder as I cannot give it on the forum).

Please note that I will stick to v13.1 (last supported version for the stratix III fpga).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I had send you a separate mail for the qar. you may check your inbox

Thanks,

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So, what is the outcome KTan9?

Is the issue still present?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry, I had been quite busy. I will test it by today.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Given that this bugs is in the older version of Quartus Prime, this bug/issue is currently in the lower priority list for Intel to fix. We apologize for any inconvenience.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I removed manually in the RTL code the lines cuda_combout_wire as sometime quartus was still not removing them for some reason.

Now it works fine.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm re-using this code again and faced the same issue (of course),

but as I wanted to use that option globally to preserve the netlist from Synplify and preserve my clock nets name point,

I'm now using this in the .qsf:

#No global optimization

set_global_assignment -name REMOVE_REDUNDANT_LOGIC_CELLS OFF

#But this is required otherwise the variable PLL clock is not working

set_instance_assignment -name REMOVE_REDUNDANT_LOGIC_CELLS ON -to "adjustable_pll:adjustable_pll_inst"

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page