- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

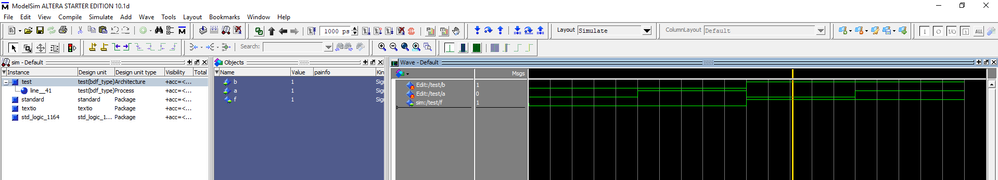

I am using Quartus II Web Edition ver. 13. I am just starting out. I am trying to simulate the following VHDL code:

-- Copyright (C) 1991-2013 Altera Corporation

-- Your use of Altera Corporation's design tools, logic functions

-- and other software and tools, and its AMPP partner logic

-- functions, and any output files from any of the foregoing

-- (including device programming or simulation files), and any

-- associated documentation or information are expressly subject

-- to the terms and conditions of the Altera Program License

-- Subscription Agreement, Altera MegaCore Function License

-- Agreement, or other applicable license agreement, including,

-- without limitation, that your use is for the sole purpose of

-- programming logic devices manufactured by Altera and sold by

-- Altera or its authorized distributors. Please refer to the

-- applicable agreement for further details.

-- PROGRAM "Quartus II 64-Bit"

-- VERSION "Version 13.0.0 Build 156 04/24/2013 SJ Web Edition"

-- CREATED "Fri Feb 08 14:19:36 2019"

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY test IS

PORT

(

b : IN STD_LOGIC;

a : IN STD_LOGIC;

f : OUT STD_LOGIC

);

END test;

ARCHITECTURE bdf_type OF test IS

BEGIN

f <= a AND b;

END bdf_type;When I run an RTL simulation, I get the following output:

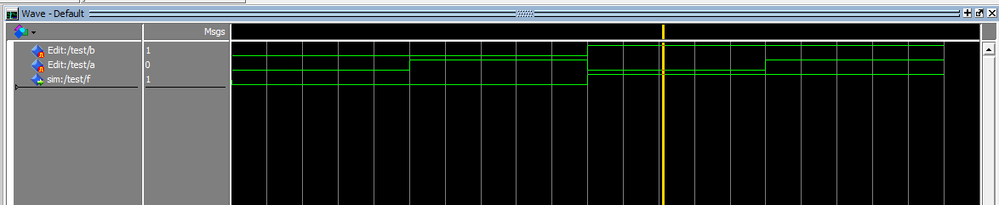

As a close-up of the waveform,

You can see that when b = 1 and a = 0, f = 1. What??

This has also been a problem in my course lab with a slightly more complex circuit. The code seems fine but the RTL simulation is not matching up.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have followed the video, which was my setup already, and have gone through the "Intel Quartus Prime Standard Edition User Guide: Third-party Simulation" part of the User Guide but I am still getting the same results. I should also add that when I download the .sof file onto my DE0 FPGA board, it does indeed show correct results.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've found that actually Reseting the simulation once or twice after simulating once (the button next to the simulation runtime textbox where you put how much time to run the simulation with the arrow pointing upwards) has solved the problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What you are reporting is very strange. Are you saying AND gate is giving a wrong functional behavior however resetting the simulation resolves it ?

Could you share the example archive with me to look into this and see what actually is happening. You may share in private message to me.

Thanks,

Arslan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page