- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

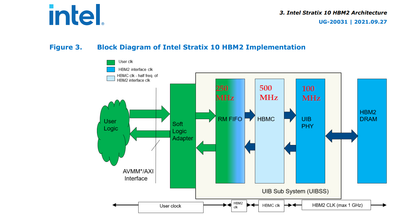

I am getting Setup Time violations on HBMC clock Domain (500MHz) due to Long Routing paths.

Type : Setup 'hbm_top_inst|iopll_t|iopll_t_outclk0'

Slack : -1.109

TNS : -863.275

Corner: Slow 900mV 100C Model

Type : Setup 'hbm_bottom_inst|iopll_b|iopll_b_outclk0'

Slack : -1.021

TNS : -1141.048

Corner: 1 Slow vid1 100C Model

Could you please suggest a fix for this issue?

Regards

Siva Kona

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @SivaKona

May I know is the timing violation fail in our Intel IP or in the design?

Best Regards,

Richard Tan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Richard Tan,

Thanks for your reply!

Setup Time Violation is in Intel IP (Quartus generated HBM IP)

My idsid is snkona, Could you please share your idsid on Teams IM, so that I can share my VNC and the Build reports.

Regards

Siva Kona

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Siva,

Following our discussion offline, problem has been root caused: HBMC IP & Quartus tool version mismatch

I’m glad that your problem has been solved. I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Regards,

Nurina

P/S: If you like my comment, feel free to give Kudos. If my comment solved your problem, feel free to accept my comment as solution!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page