- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi All,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Well, there's your problem. It's getting optimized away. Tap the "upstream" signals that drive this or add virtual pin assignments to the signal in the Assignment Editor.

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Any signal you can find in the Signal Tap Node Finder filter is tappable. It doesn't matter how it's defined in the RTL. If you are concerned about RTL signals getting optimized away, use the Signal Tap pre-synthesis filter in the Node Finder. That lets you select signals directly defined in your RTL.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

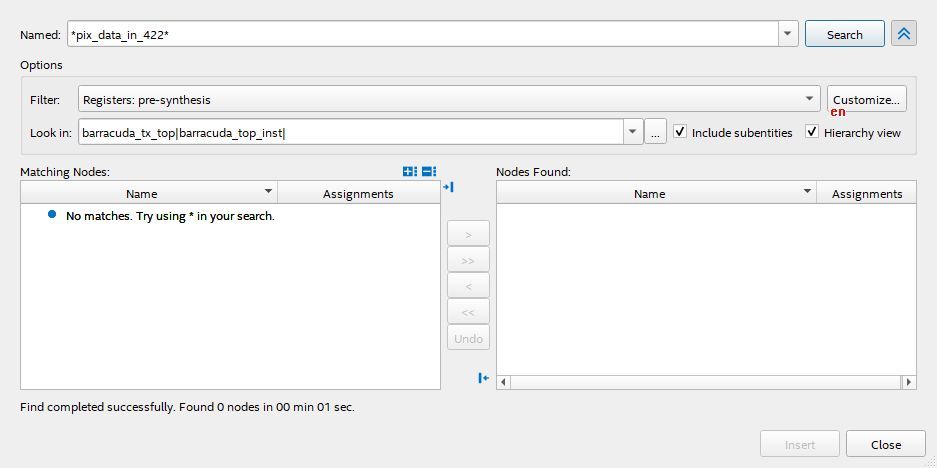

I'd like to add the pix_data_in_422 signal, to the SignalTap (signal definition please see below).

logic [PIX_DATA_BW-1:0] pix_data_in_422;

always_comb begin : pix_data_in_422_l

pix_data_in_422 = {//[95:48]

pix_data_in[47+48:40+48],pix_data_in[15+48:12+48],4'd0, // [47:32] Cr/Cb

pix_data_in[31+48:24+48],pix_data_in[11+48: 8+48],4'd0, // [31:16] Y

16'd0, // [15:0]

//[47:0]

pix_data_in[47:40],pix_data_in[15:12],4'd0, // [47:32] Cr/Cb

pix_data_in[31:24],pix_data_in [11:8],4'd0, // [31:16] Y

16'd0 // [15:0]

};

end

Here is the filter I applied in SignalTap:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

You can find any signal that mentioned in your rtl in the filter, choose pre-syn if the wire is removed

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Just to verify, you've at least run Analysis & Elaboration, if not full synthesis, before trying to use this filter, correct?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

yes, I have re-run the Analysis & Elaboration - got the same result....

I cannot understand what's the problem with the signal ....

Tried to find this signal in the RTL Viewer as well... it doesn't present there!

But, this signal does present in the simulations and the design also works on the board - without this signal the design cannot work... But Quartus how some hides it from the SignalTap and RTL Viewer.... believable...

The file with the signal is a part of the project - I checked this 1000 times !!!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Have you tried erasing the "Look in" setting in the filter? Perhaps you are searching the wrong part of your design hierarchy. Just delete that to try to search the entire design. it's got to be there.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Dmitry,

Since you saying rtl viewer also cant be seen. Can you try to add some attribute e.g no prune (prevent from removed) and take a look at rtl viewer and stp if the wire can be traced

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This is like a black magic!

I've added the "noprune" attribute to the problematic signal and also the "keep" attribute to another signal, which is driven by the problematic signal - nothing helps.... No one of them is visible neither in RTL Viewer nor in SignalTap .

Here is how I added the attributes:

logic [PIX_DATA_BW-1:0] pix_data_in_422 /* synthesis noprune */;

wire try_y422 /* synthesis keep */;

assign try_y422 = pix_data_in_422 ;

Any ideas? The file is a part of the project/compilation - I checked this in the "Files" Tab in the Project Navigation section ... I also have open the file from there and saw the above lines present in the code.

Also added this - nothing helps:

(* preserve *) reg pix_data_in_422_db;

always @(posedge pixclk_in) begin

pix_data_in_422_db <= pix_data_in_422;

end

Any ideas for the next steps?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

May I know what version of Quartus are you using?

Is is possible to use latest version and see if the wire is there and can be tapped?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I'm using Quartus Pro v19.3.0 build 200.

No, I cannot move to the latest Quartus version because the current project with its IPs is built basing on the mentioned version.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

What does pix_data_in_422 connect to? Can you tap anything else ahead of this signal that drives it or whatever it feeds into?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Actually the pix_data_in_422 signal doesn't drive any logic...

But is there a way it will not be optimized out and be able to be added to SignalTap ? None of the synthesis directives or attributes were able to prevent it from being optimized out...

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Well, there's your problem. It's getting optimized away. Tap the "upstream" signals that drive this or add virtual pin assignments to the signal in the Assignment Editor.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution and give Kudos.