- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hello,

When I generated the PLL with Quartus Prime Lite and simulated it with Modelsim, the PLL output c0, locked was "1'hz".

The correct clock waveform was confirmed for the PLL input inclk0. How can I get Modelsim to output correctly from c0, locked?

I uses v files for The source code , and I compile "pll.v", "pll_bb.v", "pll_alpll.v", "altera_mf.v" files in addition to the top module and testbench v files in Modelsim.

링크가 복사됨

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi there

Do you run enough cycles for your simulation? Have you seen any warning/error during Modelsim compilation?

thanks.

Eng Wei

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

I run enough cycles for simulation, but the PLL output c0, locked are "1'hz".

I have not seen any warning/error during Modelsim compilation.

Do I need to compile other files?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi

Are all signals that you have seen a Z is at the same hierarchy as input inclk0? Are you seeing Z for all the signals at lower hierarchy or they are at Top level of testbench?

If you can share a sample example that would be good.

Thanks.

Eng Wei

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

In your modelsim script can you try to add below lines:

view signals

run -all

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

Thank you for the advice.

I added a line to the modelsim script, but it didn't change.

The source code is a simple one created for the PLL test.

The pll_generate module is set to divide the 50MHz input clock into 25MHz.

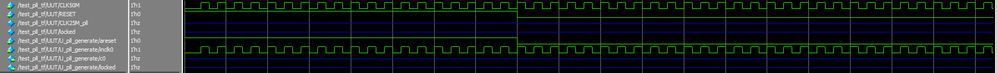

The simulation results are also attached.

Below source code

///////////////////////////////////////////////////

module test_pll(

CLK50M,

RESET

);

input CLK50M;

input RESET;

wire CLK25M_pll;

wire locked;

pll_generate U_pll_generate (

.areset (RESET ),

.inclk0 (CLK50M ),

.c0 (CLK25M_pll ),

.locked (locked )

);

endmodule

/////////////////////////////////////////////////

Below simulation result

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi there

Are you able to share your sample proj? Would like to look at your entire setup including the testbench.

Thanks.

Eng Wei

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi there

Since there's no response from you to the previous reply that have been provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Eng Wei