- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am working on Stratix10 Htile devkit, and the Quartus version I am using is Prime Pro 20.1. I am using four clocks from four dedicated transceiver ref clock pins on four tiles for the entire core through four root clock gates (intel clock control ip). After compilation, I found that there is only core clock has been promoted to be global clock. So I tried to assign the rest of the three to be global from the assignment editor. But these assignments are always ignored.

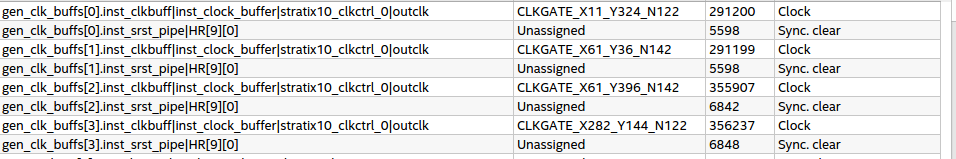

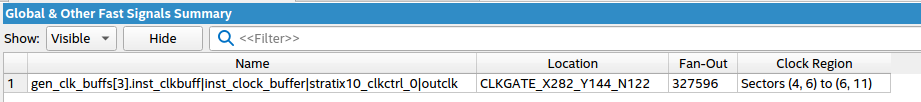

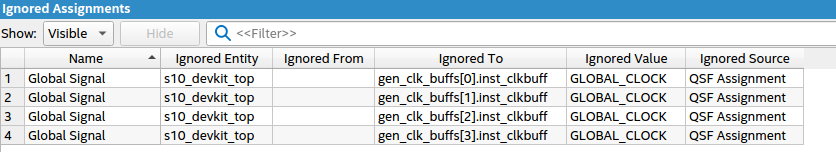

Please see the attached screen shots. I can see the four gated clocks have big number of fanouts, and the information about the promoted global clock, and the auto assigned clock region. It also can be seen that all my four global clock assignment are ignored. I didn't see any warning message about the assignment (except the assignment ignored warning, but no reason was given), and I also can see the green check mark at the each assignment from the assignment editor.

Pic 1: The high fan out signals

Pic 2 Quartus auto promoted global signal, which is one of the output of clock buffer with the most fan out

Pic 3 ignored assignments. It can be seen that all my four global clock assignments were ignored.

Is there anybody has a similar problem about the global clock assignments?

Thanks in advance for any suggestions!

Xin

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you show the actual assignments in the Assignment Editor? Perhaps the targets of the assignments are incorrect (inst_clkbuff instead of inst_clkbuff|inst_clock_buffer|stratix10_clkctrl_0|outclk) though I would think using the clock control IP, they'd be promoted automatically without requiring a manual assignment.

But you do say these are gated clocks, so where are putting the gating logic (which is usually not recommended; should use logic on clock enable control signals instead) in the clock path? Like:

input reference clock -> PLL -> clock control block -> gating logic(?) -> destinations

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sstrell,

Thank you very much for you response. The following is my global clock assignments:

set_instance_assignment -name GLOBAL_SIGNAL GLOBAL_CLOCK -to gen_clk_buffs[0].inst_clkbuff|inst_clock_buffer|stratix10_clkctrl_0|outclk

set_instance_assignment -name GLOBAL_SIGNAL GLOBAL_CLOCK -to gen_clk_buffs[1].inst_clkbuff|inst_clock_buffer|stratix10_clkctrl_0|outclk

set_instance_assignment -name GLOBAL_SIGNAL GLOBAL_CLOCK -to gen_clk_buffs[2].inst_clkbuff|inst_clock_buffer|stratix10_clkctrl_0|outclk

set_instance_assignment -name GLOBAL_SIGNAL GLOBAL_CLOCK -to gen_clk_buffs[3].inst_clkbuff|inst_clock_buffer|stratix10_clkctrl_0|outclk

The clock distribution is

input reference clock -> clock buffer (root gated clock) -> destination

I didn't add PLL yet. The reason is that it is easier to change the clock frequency using BTS on the Devkit, so that we could have a idea what core frequency we could run for our core resources. The four reference clock I am using is from the transceiver dedicated clock pins, which is recommended by the hardware designer.

You mentioned if I use the clock control IP (I set the clock control IP as a root gate), it will automatically use the global route. Should I see the information from the report of "global & other fast signal details"?

It is very interesting that I can see the high fanouts at the output of the four clock buffers from the report `plan stage -> control signals`, but I cannot see them from the report `place stage -> non global high fan out signals`, but I did see the four clock buffers from the chip planner. Since one of the output of clock buffer has been promoted to be global clock, I expect to see the rest three buffered clock in the `non global high fan out signals`. But they didn't show there, either in the "global & other fast signal details" report. I am wondering how could I know they are global or not?

My target is try to improve the fmax. We have slices, which is to implement calculation functions, connected to its corresponding transceiver. There will be 80 slices. For a single slice, it has fmax = 662MHz, and the fmax becomes 441MHz for 80 slices without any further optimization. This results is achieved when we use single clock for the entire FPGA. For the single clock, a root gate is used as well. For 80 slices, we found larger clock skews. So we try to add more clocks for the core logics to decrease the area of each clock region, so that we could improve the clock skew to improve the fmax.

Please correct me if I have some wrong concept, and let me know if you have any suggestions. I also would like to know if we are on the right direction, such as adding more core clocks, to improve the fmax.

Thanks,

Xin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

try to add -entity your_entity_name

It says that it is ignored in the GUI, may be the root cause.

Syntax Example:

set_instance_assignment -name GLOBAL_SIGNAL GLOBAL_CLOCK -to fixed_pll_altera_inst|outclk_0 -entity Achilles_arria_X

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I believe the initial inquiry has been addressed by community. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I believe the initial inquiry has been addressed. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page