- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

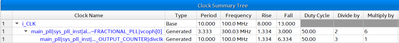

recently I found some strange behaviour of timequest STA regarding simple design with PLL on Quartus Prime Lite. If there is simple data transfer between clock (i_CLK) and clock that's output of PLL (sys_clk) (1:1 ratio "normal" mode) from same clock, then for STA setup and hold time relationshiops are dependant on waveform (phase shift) from main clock (i_CLK) that I create.

So for example in sdc:

create_clock -name {i_CLK} -period 10.000 -waveform { 0.000 5.000 } [get_ports {i_CLK}]

derive_pll_clocks

derive_clock_uncertainty

setup is 10 ns and hold is 0 ns as expected

but for constraints

create_clock -name {i_CLK} -period 10.000 -waveform { 8.000 13.000 } [get_ports {i_CLK}]

derive_pll_clocks

derive_clock_uncertainty

setup is 3.334 ns and hold -6.636 ns

From the clock tree perspective it looks like STA takes clock edges and apply it to nearest PLL VCO edge and apply that as output waveform phase shift and this leads to unrealistic timing (?) requirements that are dependand on arbitrary waveform generation in sdc, where it shouldn't be a case.

How to handle this situation - override setup/hold with set_max/min_delay ?

Moreover in Quartus Prime Pro everythink works as exptected and relation stays always the same - ts 10.0 th 0.00

Regards

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thanks for the response.

I'm checking with engineering on the consequences of using this solution, I'll let you know of any updates.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Engineering has provided a solution. I will attach the .sdc file.

Please use this .sdc file in place of derive_pll_clocks.

You may receive a warning "PLL cross checking found inconsistent PLL clock settings." which you can ignore.

For future references, what I've done is:

- On Timing Analyzer, run derive_pll_clocks and then run write_sdc -expand myexpanded.sdc

- On the create_generated_clock -name {*|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|vcoph[0]} add an offset so that the rising edge of this clock matches the rising edge of the base clock that feeds into the PLL.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I can't attach the .sdc file, but here's the sdc commands for -waveform {8.000 13.000}

##**************************************************************

## Create Clock

##**************************************************************

create_clock -name {i_clk} -period 10.000 -waveform { 8.000 13.000 } [get_ports {i_clk}]

#

##**************************************************************

## Create Generated Clock

##**************************************************************

#

create_generated_clock -name {project_pll|pll_in_normal_mode_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|vcoph[0]} -source [get_pins {project_pll|pll_in_normal_mode_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|refclkin}] -duty_cycle 50/1 -offset 6.666 -multiply_by 6 -divide_by 2 -master_clock {i_clk} [get_pins {project_pll|pll_in_normal_mode_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|vcoph[0]}]

create_generated_clock -name {project_pll|pll_in_normal_mode_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|divclk} -source [get_pins {project_pll|pll_in_normal_mode_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|vco0ph[0]}] -duty_cycle 50/1 -multiply_by 1 -divide_by 3 -master_clock {project_pll|pll_in_normal_mode_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|vcoph[0]} [get_pins {project_pll|pll_in_normal_mode_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|divclk}]

#

##**************************************************************

## Set Clock Latency

##**************************************************************

#

#

#

##**************************************************************

## Set Clock Uncertainty

##**************************************************************

derive_clock_uncertainty

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you also share the design you have used for Pro?

This is for the engineering team so they can refer to it.

I am seeing problems from my end somehow.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks for the reply and some solution.

Regarding Quartus Pro I'll try to add qar file @ monday as for today I don't have access for that version.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Have you tried the solution?

Can you provide the .qar file for Pro?

Thanks,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have received feedback from engineering team that the design for Pro version is not needed anymore.

Therefore since your problem has been addressed, I now transition this thread to community support. If you have a new question, please login to https://supporttickets.intel.com , view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution, give Kudos and rate 4/5 survey

Regards,

Nurina

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »