- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have two questions about Timing Analyzer.

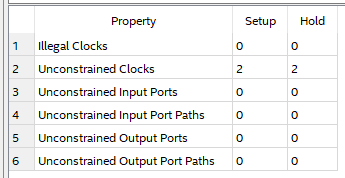

1. As show in the fig, Quartus reminds me that I have two Unconstrained Clocks, But these two are not clock signals in my design, how can I correct them?

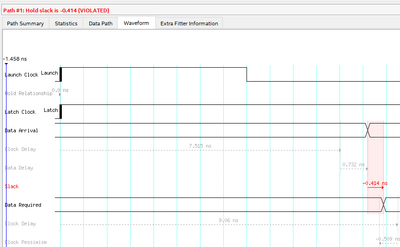

2.If I have a hold violation in my project, as shown in the figure, how can I fix it?

Can I fix it by adding a delay cell? How can I add a delay cell to my data path?

I appreciate your help very much.

O.Chiang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I know where the problem is.

Because my design accidentally synthesized a latch, and these two signals are connected to latch_en, Quartus regards these two signals as clock.

When I removed the latch, the situation was resolved.

Thank you very much for your help.

O.Chiang

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You don't mention what clocks the tool is telling you are unconstrained. What are they? If it's the JTAG clock, look at this:

As for the hold timing issue, without seeing the design or the .sdc (or even knowing what path is failing timing), this isn't really possible to solve. It looks like you're going between two different clock domains and maybe need multicycle, but it's impossible to tell for sure.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, thanks for your reply

About the first question. I mean, Quartus mistaken the signal for a clock signal, in fact he told me that the two Unconstrained signals are not a clock signal in my design. Those two signals are just normal Register output's data.

Regarding the second question. I found my mistake after your hint, maybe I only need to set the path to false path, thank you very much!

I appreciate your help very much.

O.Chiang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I know where the problem is.

Because my design accidentally synthesized a latch, and these two signals are connected to latch_en, Quartus regards these two signals as clock.

When I removed the latch, the situation was resolved.

Thank you very much for your help.

O.Chiang

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page