- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

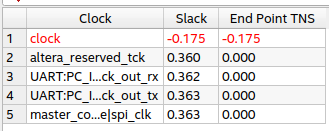

my current Design has a TNS of 0.175ns which i cant get rid of.

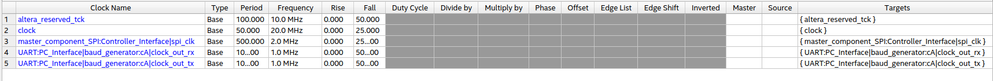

i tried to constrain all of my paths with some reasonable values:

But no matter what i enter for the four "user" clocks the TNS on clk stays at 0.175ns (since im just validating a concept i can adjust the clock speeds to my liking but i try of course to use realistic values.) Since the altera_reversed_tck is auto generated i did not touch it, but with the other i tried a variety of Values with absolutely no effect on the TNS.

The failling Path is this one:

What am i missing here?

Thanks in Advance

Matthias

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Without seeing the complete timing report for that path (full path detail level), you have a relatively large clock skew there. You're transferring data between two clock domains (spi_clk to clock), so perhaps you need multicycle timing constraints or to add registers. Is this within an IP or just your own logic? More detail about the failing path and your design needed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Does above reply help?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We did not receive any response to the previous question/reply/answer provided, thus I will put this case to close pending. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

Regards,

Nurina

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page