- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello all,

I am using Quartus Prime Lite Edition, versions 17.0 and 18.1, and the respective bundled ModelSim Intel FPGA Starter Edition 10.5b on Linux.

I'm struggling to simulate Quartus VHDL designs which include an FFT IP Core instance. As long as this core is not included, everything runs fine, I can use NativeLink to generate Tcl scripts, automatically launch my testbench in ModelSim and the simulation runs fine. But as soon as I include the FFT IP Core and run NativeLink, the compilation within ModelSim eventually breaks with messages like:

# ** Error: (vsim-3033) [...]/db/ip/myfft/submodules/myfft_fft_ii_0.sv(52): Instantiation of 'auk_dspip_r22sdf_top' failed. The design unit was not found.Many of the submodule files are compilable, but some are obviously not. This happens also when I try to compile the testbench environment that is generated by Qsys / Platform Designer. (You can find the full ModelSim transcripts as attachments.) However, synthesis in Quartus runs without any error.

Then I tried a simple "official" example from https://fpgawiki.intel.com/wiki/DSP_Basic_Design_Examples with my ModelSim installation that came with Quartus 17.0. This example is a readily generated project, so I only have to invoke ModelSim and try to follow the steps. In this example, compilation in ModelSim breaks within the "ld" step (full transcript attached as "msim_transcript_fftifft_170.txt"):

# Model Technology ModelSim - Intel FPGA Edition vlog 10.5b Compiler 2016.10 Oct 5 2016

# Start time: 19:54:38 on Oct 05,2018

# vlog -reportprogress 300 ./../submodules/mentor/apn_fft_mult_cpx_1825.v -work fft_ii_0

# ** Fatal: Unexpected signal: 11.

# ** Error: ./../submodules/mentor/apn_fft_mult_cpx_1825.v(38): in protected region

# End time: 19:54:38 on Oct 05,2018, Elapsed time: 0:00:00

# Errors: 2, Warnings: 0

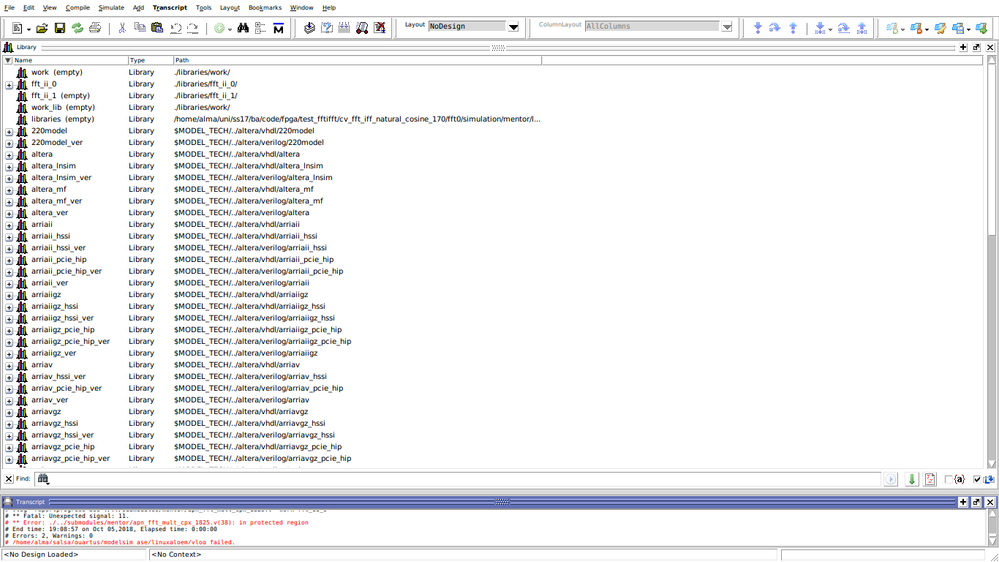

# /home/alma/salsa/quartus/modelsim_ase/linuxaloem/vlog failed.Since in this example, nothing was to be generated by my Quartus software, it seems that something in my ModelSim installation is missing. Here is a screenshot with the upper half of the available libraries:

Can you push me into the right direction, where to locate my error? Right now I don't know how to find out what I'm doing wrong.

If you need more information, please let me know.

Thank you and best regards,

Alex

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

To get this design to simulate correctly , you need to compile the following files in order.

1. From the /simulation folder - the top-level fft design .v file

2. From the /simulation/submodules folder –

a. All of the _pkg.vhd files first

b. Then the _roundsat.vhd file

c. Followed by the rest of the .vhd files

3. Next, compile the files in the /simulation/submodules/mentor folder-

a. The Verilog files (there are only 2 of them)

b. All of the pkg files first

c. Then the apn_* VHDL files

d. Followed by the asj_* VHDL files -> except the asj_fft_sglstream. This one needs to be compiled last.

e. Next compile the rest of the files auk_* VHDL

f. Lastly compile the asj_fft_sglstream.vhd file.

4. All of the files should be compiled successfully and you should be able to see them in the work folder.

Now simulate the top-level module of the design or testbench. It will load successfully

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alex,

I looked at the log files you shard and tried to simulate the design my self too. I didn't see any Errors.

I followed the steps as below.

- As for the design example from the link you shared I downloaded Cv_fft_iff_natural_cosine_170.zip and simulate by executing "msim_setup.tcl" > ld from directory "cv_fft_iff_natural_cosine_170\fft0\simulation\mentor"

- I did generated a small test design to simulate the FFT IP standalone, and simulated using the autogenerated script "msim_setup.tcl" I didn't see any Error there too. Can you try this on your end ?

Also your Modelsim libraries looks fine to me, as files giving Error in simulation are from IP files in local directory..

Thanks,

Arslan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page