- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ENTITY For_V1 IS PORT(

SCLK_SLAVER : IN std_logic;

testpin : OUT std_logic

);

END For_V1;

ARCHITECTURE circuit OF For_V1 IS

signal clk : std_logic:=SCLK_SLAVER;

BEGIN

process(SCLK_SLAVER)

begin

if SCLK_SLAVER'event and SCLK_SLAVER = '1' then

clk <= not clk;

end if;

end process;

testpin <= clk;

END circuit;

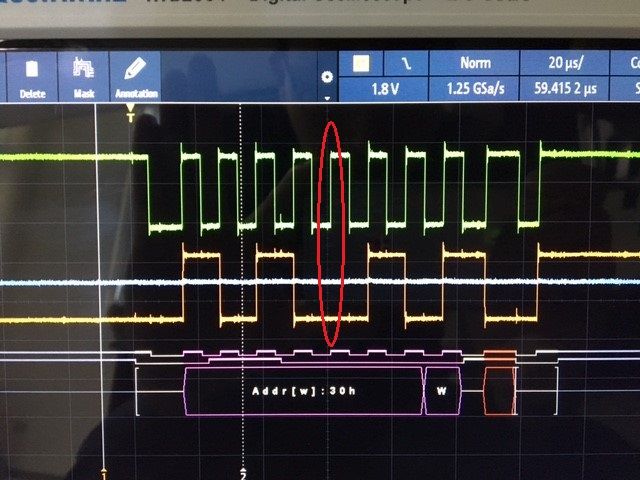

I find clk pin is not able to catch rising edge of SCLK_SLAVER every time, I am so confused with it.

could anyone give me a suggestion for it to fix the problem?

clock rising time:60~90ns

clock frequency : 80K

Green lin is SCLK_SLAVER

orange line is testpin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

SCLK from I2C or SPI are notoriously bad for using as clocks It is much better to treat SCLK as any other signal and sample it inside the FPGA with a much faster clock, and use the edge of SCLK as a clock enable for your other registers that also use a proper system clock.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Where does SCLK_SLAVER come from? a crystal or PLL?

If it is a logic generated clock then it can be possible that it is effected by high skew and temperature variability.

What is clk meant to drive? IS it driving internal logic?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

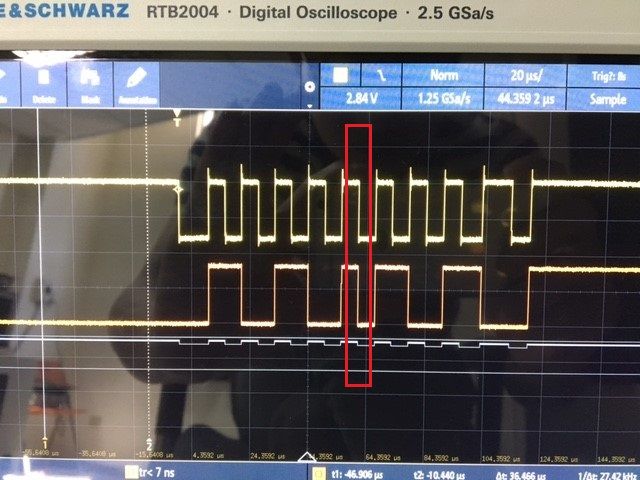

SCLK_SLAVER come from MCU, Actually it is a I2C clock.

At first I build an I2C communication between MCU(master) and FPGA(slave) but it didn't work stably, so I simplified my code into two signals(SCLK_SLAVER and testpin ) to debug and find the issue.

Voltage level of I2C clock is 3.3V and my FPGA I/O pin setting 3.3 LVCOMS .

By the way, sometime it is triggered by falling edge, I don't figure it out what happen.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

SCLK from I2C or SPI are notoriously bad for using as clocks It is much better to treat SCLK as any other signal and sample it inside the FPGA with a much faster clock, and use the edge of SCLK as a clock enable for your other registers that also use a proper system clock.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page