- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am trying to read and write 8-bit Counter data Using Quartus and NIOS.

In SOPC : I am assigning PIO : 1-bit input for enable

PIO : 8-bit output for out

module Counter_Top_Level_design

(

input clk, rst_n,

output wire[7:0] out

);

wire enable;

always @ (posedge clk or negedge rst_n)

begin

if (~rst_n)

out <= 0;

else if (enable == 1'b1)

out <= out + 1;

end

NIOS_SYSTEM niosii_system_inst (

.clk_clk (clk ), // clk.clk

.reset_reset_n (rst_n ), // reset.reset_n

.output_pio_export ( enable ), // output_pio.export

.counter_out_export (out)

);

endmoduleI am getting an Error message :

Error (10137): Verilog HDL Procedural Assignment error at Counter_Top_Level_design.v(11): object "out" on left-hand side of assignment must have a variable data type

Error (10137): Verilog HDL Procedural Assignment error at Counter_Top_Level_design.v(13): object "out" on left-hand side of assignment must have a variable data type

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

output port "out" must have reg data type so replace "output wire[7:0] out" with "output reg[7:0] out"

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Best Regards

Vikas Jathar

(This message was posted on behalf of Intel Corporation)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

module Counter_Top_Level_design

(

input clk,

output reg[7:0] out

);

always @(posedge clk)

begin

out <= out + 1;

end

NIOS_SYSTEM niosii_system_inst (

.clk_clk (clk ), // clk.clk

.reset_reset_n (rst_n ), // reset.reset_n

.counter_out_export (out)

);

endmoduleI have assigned PIO (output):8 bit, its showing error. If i assign PIO (input):8 bit error not coming. But i want to read the counter data.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Have you resolved the issue?

If not, please provide the project file if possible.

Best Regards

Vikas Jathar

(This message was posted on behalf of Intel Corporation)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

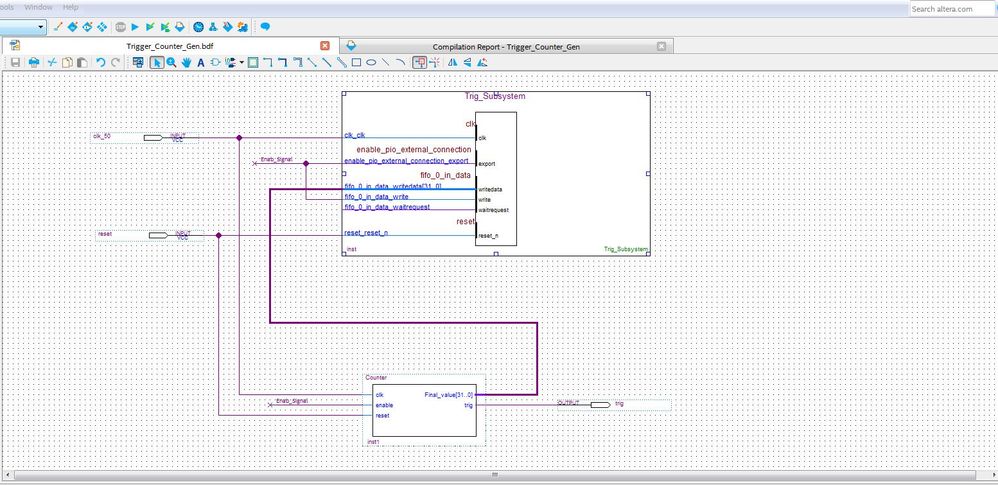

Hello, Instead of PIO. Now i am using AVALON On-chip FIFO Memory Core.

Still my issue have not solved. Please help me 😨

I am getting Proper answer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, I am not getting the result.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page