- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi everyone,

I've generated PLL by Quartus 18.1 Lite MegaWizard .(C0,100Mhz-> 125MHz).

Then I've built a very simple project in ModelSim 10.5B with above mentioned PLL component.

But when I'm trying to simulate the project, I'm getting a such kind warning:

"Warning: (vsim-8684) No drivers exist on out port /altpll_0001_tb/UUT1/CLK_OUT".

it seems that ModelSim cannot recognize a MegaWizard generated component...

What Should I do?

P.S. I've attached a project to this message

Link kopiert

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Alex,

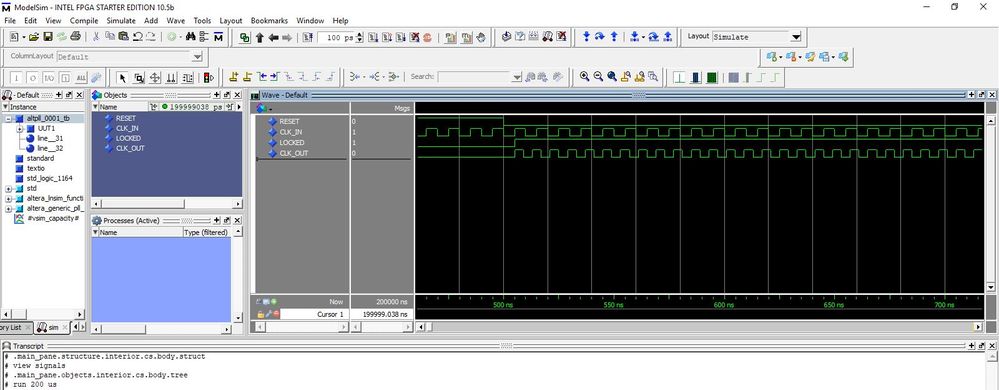

You can ignore the warnings, BTW are you getting desired result in simulation?

please provide screenshot.

Let me know, If you have any different concern.

Regards,

Vicky

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi,

Can you please check with Native link simulation?

https://www.youtube.com/watch?v=PmVVXQchv2c

this issue may occur when simulation process missing any file or sequence.

refer the attachment using Native link.

Regards,

Vicky

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Vicky,

I've made successful simulation with ALTPLL core for Cyclone-4 with Native Link .

But when I'm trying to execute simulation with PLL core for Cyclone-5, then I'm getting such error:

# ** Error: (vcom-7) Failed to open design unit file "C:/Alex/my_designs/18_1/PLL/PLL_001/cyclone_V/PLL_50MHz.vho" in read mode.

# No such file or directory. (errno = ENOENT)

# End time: 13:11:25 on May 13,2019, Elapsed time: 0:00:00

# Errors: 1, Warnings: 0

# ** Error: C:/intelFPGA_lite/18.1/modelsim_ase/win32aloem/vcom failed.

# Error in macro ./PLL_001_run_msim_rtl_vhdl.do line 8

# C:/intelFPGA_lite/18.1/modelsim_ase/win32aloem/vcom failed.

# while executing

# "vcom -93 -work work {C:/Alex/my_designs/18_1/PLL/PLL_001/cyclone_V/PLL_50MHz.vho}"

In addition I'm sending you another project with PLL.

What file or sequence is missing?

P.S. I've made simulation of LPM_counter with Native link for Cyclone 5 component and it works successfully...

Maybe the problem with Cyclone5 pll?

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Vicky,

I've received the project and simulated it.

It works properly.

Now , explain me please what did you change at the code?

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi,

I haven`t changed anything in your project, just performed the simulation using native link settings as suggested in my second post.

As I told earlier, it might happen due to all modules/submodules are not in single directory so here in case of native link script will take care of that.

Should I consider that case to be closed?

Regards,

Vicky

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi,

off course it is available. As I told earlier, create project in ModelSim which consists of design (All, top & submodules) & testbench in single directory( for simplicity).

In case of IP, create/generate the HDL file for that & add into ModelSim project & Perform Compilation, Simulation.

Regards,

Vicky

- RSS-Feed abonnieren

- Thema als neu kennzeichnen

- Thema als gelesen kennzeichnen

- Diesen Thema für aktuellen Benutzer floaten

- Lesezeichen

- Abonnieren

- Drucker-Anzeigeseite