- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

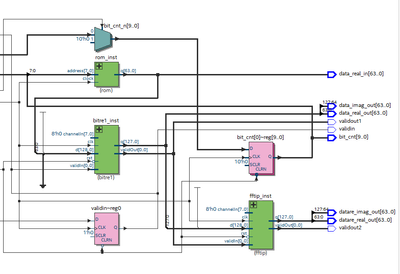

Recently, I designed a double-precision floating-point FFT project using Quartus Prime 21.1. This project includes 1-PORT-ROM IP, Bit-Intel FPGA IP and FFT Intel IP.

ROM IP outputs 1024 64-bit double precision floating-point numbers, which are sinusoidal signals with amplitude of 100 and frequency of 200. ROM data is real part input of FFT IP,and the imag part input is 64'd0.

Data flows into Bit-reverse Intel FPGA IP before it flows into FFT Intel IP.

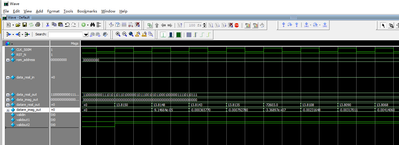

In theory, the output of the FFT should be such that at frequency 200 the amplicon is 100.

HOWEVER, the output of FFT in Modelsim is much larger than 200 at a frequency of 200 and it is not 0 at other frequency components.

I wonder where I went wrong in design. If you know, can you please tell me? Thank you!!!

Link Copied

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page