- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Intel Support/Expert,

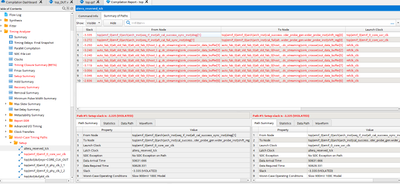

I am compiling hip_a10gx_g3x8_avmm_dma256_1602 with Quartus Prime Pro 21.3. after update the IP and minor tune up, it compiles. but it has few timing analysis failures.

most of the failure is the signal between the launch clock top|emif_0\emif_0_core_usr_clk and latch clock altera_reserved_tck

couldn't find altera_reserved_tck in the design because it is a hidden signal. if it is for the system configuration only, I don't think it has any relation to emif interface, in this case, is it reasonable to set these clock pair as false path? if not, how to optimize this path timing?

thank you very much

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I routinely include these commands in my .sdc file to mitigate timing paths related to the system clock and the JTAG clock:

# setup JTAG clock

set_false_path -from [get_ports {altera_reserved_*}] -to CPUCLK

set_false_path -from CPUCLK -to [get_ports {altera_reserved_*}]

create_clock -name altera_reserved_tck -period 40 {altera_reserved_tck}

remove_input_delay [get_ports {altera_reserved_tdi altera_reserved_tms}]

set_input_delay -clock altera_reserved_tck -clock_fall 3 [get_ports {altera_reserved_tdi altera_reserved_tms}]

remove_output_delay [get_ports {altera_reserved_tdo}]

set_output_delay -clock altera_reserved_tck 3 [get_ports {altera_reserved_tdo}]

# Cut off paths between async clock domains

remove_clock_groups -all

set_clock_groups -asynchronous -group {CLOCK_50} -group {CPUCLK} -group {altera_reserved_tck}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Does the above comment help?

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

don't have a chance to try it during the holiday season. will give it a shot asap. thank you very much for all the helps.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from community or Intel support are helpful, please feel free to mark as solution, give Kudos and rate 4/5 survey

Regards,

Nurina

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page