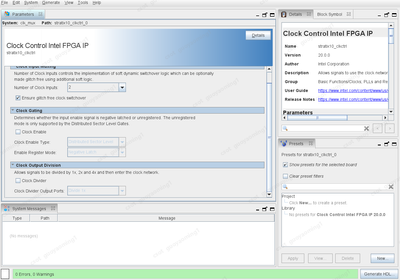

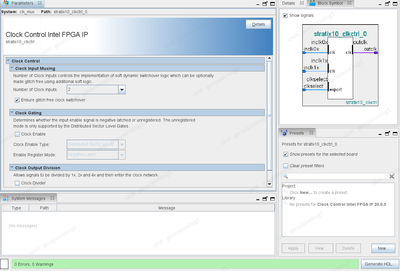

I have created a project in quartus prime pro 23.4 ant I have used clock control intel FPGA IP as a MUX for clock.And When I run synthesis error encouted.

Error(13224): Verilog HDL or VHDL error at clk_mux_stratix10_clkctrl_2000_yem6tmi.v(67): index 1 is out of range [0:0] for 'clkselect'

And sorry my computer cannot upload any picture

Below is the detail part of clk_mux_stratix10_clkctrl_2000_yem6tmi.v module module

module clk_mux_stratix10_clkctrl_2000_yem6tmi_clksel_mux (

input inclk0x,

input inclk1x,

input clkselect,

output clkout

);

parameter num_clocks = 2;

genvar i;

wire [num_clocks-1:0] clk;

wire [num_clocks-1:0] clk_select; // one hot

reg [num_clocks-1:0] ena_r0;

reg [num_clocks-1:0] ena_r1;

reg [num_clocks-1:0] ena_r2;

wire [num_clocks-1:0] qualified_sel;

// A look-up-table (LUT) can glitch when multiple inputs

// change simultaneously. Use the keep attribute to

// insert a hard logic cell buffer and prevent

// the unrelated clocks from appearing on the same LUT.

assign clk[0] = inclk0x;

assign clk[1] = inclk1x;

// Decoder logic

assign clk_select[0] = ~clkselect[1] & ~clkselect[0];

assign clk_select[1] = ~clkselect[1] & clkselect[0];

链接已复制

9 回复数

Thanks, I know what this message means , but this V file is automatically created by QUARTUS prime ,which is why i am confused

Thanks, I know what this message means , but this Verilog file is automatically created by Quartus prime ,which is why i am confused