- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello.

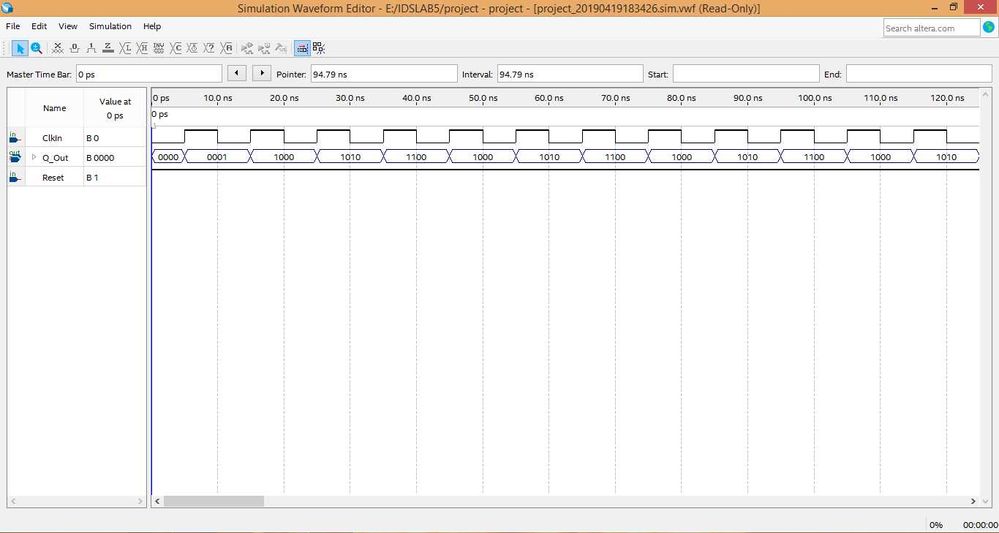

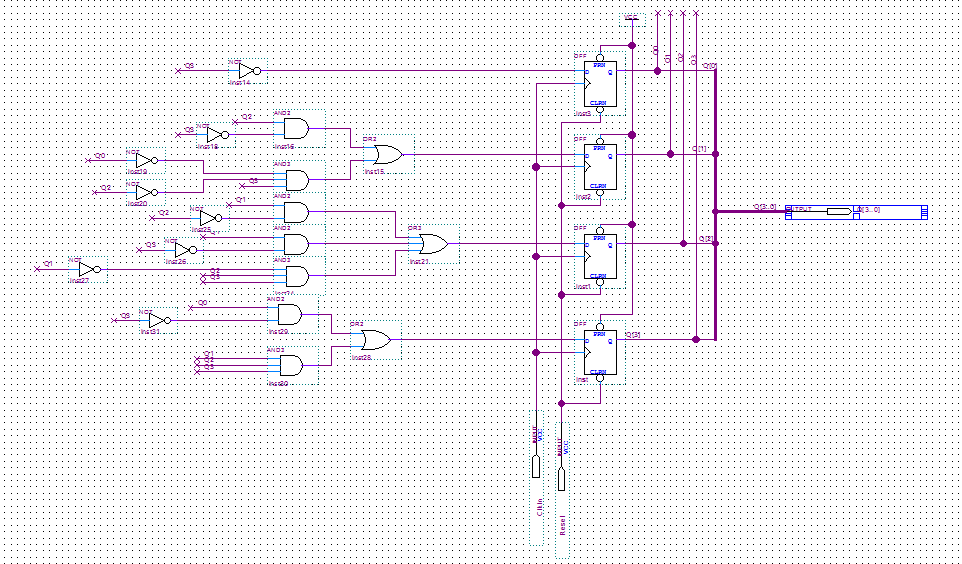

i'm a bit of a newbie here and i'm trying to create a bcd counter schematic for a university project using either a tff or a dff. i created the truth table for the circuit and designed the circuit as it should be. but when i start the simulation, it doesn't count from 0-9 but instead it just goes from 0 to 1 then 8 and 9 i cannot find an issue with the circuit but i thought someone with experience should know. i have attached a screenshot of the circuit (i can't upload the bdf file) and

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This seems an Homework, again schematic is the basic approach to initial learning of FPGA but deprecated, useful if you need convert old discrete logic design.

Your design has error in it and state network nor work on logic nor on simulator.

Previous sentence infer nor on FPGA, check for error and retry.

First error is on top, Q0 must be excited by NOT Q0 not Q3..

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Have you compiled the design without any error?

If possible, attach the project file.

"Project" -> "Archive Project"

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi vicky.

i did compile it and got no errors. but my project is a bit big so i'll be sending the bdf file of the bcd counter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Click(Highlight) "Q" in Simulation Waveform Editor.

"Edit"->"Radix"-"Unsigned Decimal"

It is counting (0-15) since your design(logic) consist of 4 flops, just modify the design as per requirement.

let me know, if this has helped to resolve your issue or if you have any different concern

Regards,

Vicky

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i found what was wrong. as @RRomano001 suggested. i had my most and lest significant bits switched, that's why it wasn't right. But now i'm trying to expand it into a digit counter by adding wires from Not Q[0], Q[1], Not Q[2] and Q[3] connected to AND4 logic gate so that when we get 1010 it will feed into the next counter and give us the next digit which is not doing so. i'm thinking it's the wire placement that is wrong. do you have any idea where to add them

thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Gabra, sorry say this but I fear you need grasp digital design in deep as i usually told my pupils, error come from everywhere.

A BCD counter never count to 1010 that is ten decimal but remain in BCD domain {0..9} .

You can apply this method to ripple carry asyncronous reset but not to a syncronous counter as your appear to be.

This case require an enable count that happen on last digit value, when counter is 9 then load 0 as next state, at same time enable count on next digit. Your design miss this feature.

I suggest you start learning an HDL language and do this in a more simple fashion using state machine. I am proficient on VHDL and just read and understand Verilog I don't like so much, in HDL your design can be:

signal BCD : Std_Logic_Vector(3 downto 0);

signal enable : Std_Logic := '1'; -- enable count

signal sreset : std logic := '0'; -- reset to 0 clock gated

BCD_counter: process (clock, reset_n)

var count : integer range 0 to 9 := 0;

if reset_n = '0' then

count := 0; -- async reset

else

If rising_edge(clock, reset_n) then

BCD <= Std_Logic_Vector(to_unsigned(count, 4));

if enable = '1' then

if count = 9 or sreset = '1' then

Count := 0;

else

count := count +1;

end if; -- counter

end if; -- enable

end if; -- edge

end if; -- reset

end process;

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello again.

i know i'm not that knowledgeable when it comes too the digital systems part, but i'm doing my best with my limited time. and i end up getting to what i was looking for. but my problem is that we have this week off and i can't gt in contact with the lab assistants, plus the lecturer doesn't provide enough explanations to everything and with my limited knowledge, it takes some time to grasp it. but if only i can get you to help me for the last time. i'm at the last part of my circuit and i have all my parts ready. a part with bcd counter and a part with a digit shifter where it changes the locations of the digits on my fpga. but the thing is, i'm trying to connect them so that i can switch them with one button push, it worked but i have to hold the button to keep the shifter not just press it. i'm not quite sure what we need to use here, i'm thinking of a 2 to 1 multiplexer but then i'm not sure how to connect it.

i have attached all my project for you to check it and have more freedom working around it. if you could help me i appreciate it, if not, i understand.

thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

as hint try this link:

http://www.pyroelectro.com/edu/fpga/

or this one

also try this software and learning guide from my friend Giuliano Donzellini:

https://www.digitalelectronicsdeeds.com/

Have fun.

Roberto

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I got eye on it.

Compile to 2 LE so a lot of design error can be on it or I am wrong , I don't use schematic nor Cyclone IV so may be some setting where lost on conversion.

When you have your lecturer again on lab, show the link I sent to you, may be it find more useful than try use Quartus in Archaic mode.

BCD Counter still have trouble, ripple counter clock are to be avoided on FPGA, enable is missing and also next counter has to increment from 9 to 0 transition not from 0 to 1.

BCD decoder has more sense on output multiplexer than on every digit, this is not a big issue. Just use one at output where you drive multiplexed display.

Note: may be synthesis do it for you, but you have to learn good practice.

An LED display don't like to be driven @50/4-> 12.5MHz so reduce to a reasonable frequency, scale clock to 10KHz or less.

I see you didn't grasped enough logic design, try use DEEDS I suggested, you can single step clock and see every point of the circuit probing level or display value all in real time. This is targeted to learn digital design @college and high school too.

Tool export design to Altera Quartus and selected board, enjoy it.

Your design required 44 second to compile, I fear on a non Linux or MAC took some minutes so this waste a lot of time.

Sorry I cannot debug your homework, you need use a good textbook, if still available at Logic gate time I adopted Floyd Digital design, old book

https://www.amazon.com/Digital-Fundamentals-Global-FLOYD-THOMAS/dp/1292075988/ref=dp_ob_title_bk

If you are at college course Deeds book is more close:

browse college site and subscribe to, you may get more help than where we are busy with deadline of release project.

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello. Thank you for all your assistance. I do appreciate it. I know my knowledge is limited in this subject and my methods are primitive, but as long as it shows correctly on the fpga i will get full mark. My biggest problem is that my lecturer is bad at teaching, he knows everything so he thinks we all should know it too. If i compare this subject to driving a car, what he does is teching us how to build car parts and then asking us to drive it. See where i'm going with that. I can't even ask classmates for help because i'm the one who knows more than everyone. My test is next monday and he demands us to do stuff never mentioned in the lecture, like how to build a bcd counter with a parallel load, i tried googling it but as you said, no one use schematics while we are forced to use it. Anyway, i'm definitely getting a 70% mark on that project which is nice. Also i would like to thank you for your time trying to help me even though i'm useless lol.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry for misunderstood, here we are professional seeking for "Exchange" or hint, didn't mean you are useless nor wrong, you welcome but just too early to interact here.

I was trying say to you this channel is wrong for learning when at too basic level, I suggested you college channel where you can interact other pupils and learn from what we teach.

Remember I am not paid to teach for free nor other can do and never we can do homework for free, this sound as stopping teacher/professional work like me or colleague at other sides.

(ZEN) Also it is useless and bad to criticize your lecturer, in my point of view still is a colleague and when you as pupils do a criticism to my colleague I can think you do same for me...

Sometimes I see some my colleague perform bad but remember deontological ethics tell me to not confirm and forever protect them in front of an attack right or odd. (IEEE rule too)

Also please be coherent, I sent you a couple of link where you can find help, Pyroedu and FPGA4Fun both have teaching materials and discussion on how to build counters, Deeds site devoted to teaching has material on topics.

Both book and course too start from Logic gates, they use a special (free) tool customized for teaching Logic design.

What is wrong with lecturer or pupils has to be left behind your college, please avoid do it in public, at least do in PM.

Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page