- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi below is my code, it simulated perfectly but when i want to check the outputs using the .VWF file i am getting the following errors which are listed at the bottom. i am using Altera Stratix® V GX FPGA (5SGXEA7N2F45C2)

code:

module data_transfer(

input clk,

output [0:0] tx_serial_data

);

reg [79:0] tx_pma_parallel_data = 80'h2451BE17A3;

reg reset = 0;

wire [139:0] reconfig_to_xcvr;

wire [91:0] reconfig_from_xcvr;

wire reconfig_busy;

wire [31:0] reconfig_mgmt_readdata;

wire reconfig_mgmt_waitrequest;

wire clkout;

wire pll_powerdown;

wire tx_analogreset;

wire tx_digitalreset;

wire tx_ready;

wire tx_cal_busy;

/*trans_rec tx_transrec (

.pll_powerdown(pll_powerdown), // low

.tx_analogreset(tx_analogreset), // off and add Transceiver PHY Reset Controller

.tx_digitalreset(tx_digitalreset), // off and add Transceiver PHY Reset Controller

.tx_pll_refclk(clk), // refclk

.tx_pma_clkout(clkout), // clkout

.tx_serial_data(tx_serial_data), // data

.tx_pma_parallel_data(tx_pma_parallel_data), // tx_pma_parallel_data.tx_pma_parallel_data

.pll_locked(), // low

.tx_cal_busy(tx_cal_busy), // out_busy

.reconfig_to_xcvr(reconfig_to_xcvr), // reconfig_to_xcvr.reconfig_to_xcvr

.reconfig_from_xcvr(reconfig_from_xcvr) // reconfig_from_xcvr.reconfig_from_xcvr

);*/

trans_reconfig recofig (

.reconfig_busy(), // reconfig_busy.reconfig_busy

. mgmt_clk_clk(clk), // mgmt_clk_clk.clk

.mgmt_rst_reset(), // low

.reconfig_mgmt_address(), // reconfig_mgmt.address

.reconfig_mgmt_read(), // .read

.reconfig_mgmt_readdata(), // .readdata

.reconfig_mgmt_waitrequest(), // .waitrequest

.reconfig_mgmt_write(), // .write

.reconfig_mgmt_writedata(reconfig_mgmt_writedata), // .writedata

.reconfig_to_xcvr(reconfig_to_xcvr), // reconfig_to_xcvr.reconfig_to_xcvr

.reconfig_from_xcvr(reconfig_from_xcvr) // reconfig_from_xcvr.reconfig_from_xcvr

);

reset_cont reset_controller (

.clock(clk), // clock.clk

.reset(reset), // reset.reset

.pll_powerdown(pll_powerdown), // pll_powerdown.pll_powerdown

.tx_analogreset(tx_analogreset), // tx_analogreset.tx_analogreset

.tx_digitalreset(tx_digitalreset), // tx_digitalreset.tx_digitalreset

.tx_ready(tx_ready), // tx_ready.tx_ready

.pll_locked(), // pll_locked.pll_locked

.pll_select(), // pll_select.pll_select

.tx_cal_busy(tx_cal_busy), // tx_cal_busy.tx_cal_busy

.rx_analogreset(), // rx_analogreset.rx_analogreset

.rx_digitalreset(), // rx_digitalreset.rx_digitalreset

.rx_ready(), // rx_ready.rx_ready

.rx_is_lockedtodata(), // rx_is_lockedtodata.rx_is_lockedtodata

.rx_cal_busy() // rx_cal_busy.rx_cal_busy

);

endmodule

error:

Completed successfully.

**** Running the ModelSim simulation ****

C:/intelFPGA/16.1/modelsim_ase/win32aloem/vsim -c -do data_transfer.do

Reading C:/intelFPGA/16.1/modelsim_ase/tcl/vsim/pref.tcl

# 10.5b

# do data_transfer.do

# ** Warning: (vlib-34) Library already exists at "work".

# Model Technology ModelSim - Intel FPGA Edition vlog 10.5b Compiler 2016.10 Oct 5 2016

# Start time: 12:02:55 on Jul 29,2020

# vlog -work work data_transfer.vo

# -- Compiling module data_transfer

#

# Top level modules:

# data_transfer

# End time: 12:02:55 on Jul 29,2020, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

# Model Technology ModelSim - Intel FPGA Edition vlog 10.5b Compiler 2016.10 Oct 5 2016

# Start time: 12:02:55 on Jul 29,2020

# vlog -work work Waveform.vwf.vt

# -- Compiling module data_transfer_vlg_vec_tst

#

# Top level modules:

# data_transfer_vlg_vec_tst

# End time: 12:02:55 on Jul 29,2020, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

# vsim -novopt -c -t 1ps -L stratixv_ver -L altera_ver -L altera_mf_ver -L 220model_ver -L sgate_ver -L altera_lnsim_ver work.data_transfer_vlg_vec_tst

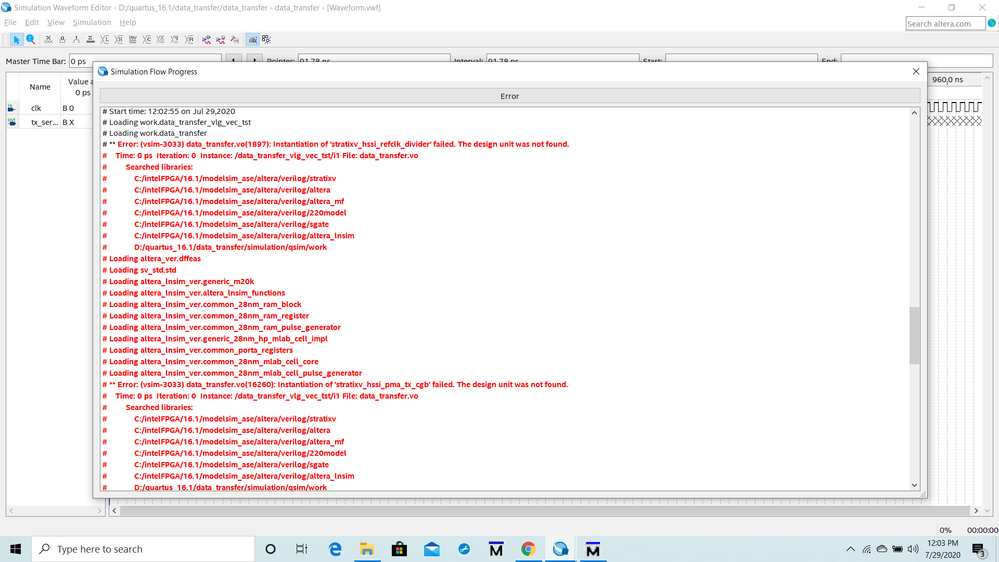

# Start time: 12:02:55 on Jul 29,2020

# Loading work.data_transfer_vlg_vec_tst

# Loading work.data_transfer

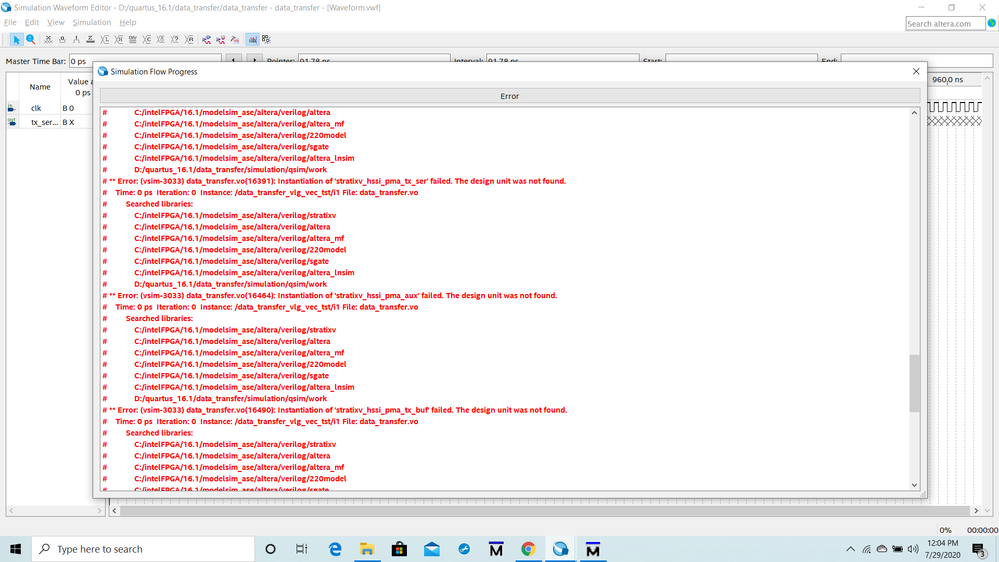

# ** Error: (vsim-3033) data_transfer.vo(1897): Instantiation of 'stratixv_hssi_refclk_divider' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /data_transfer_vlg_vec_tst/i1 File: data_transfer.vo

# Searched libraries:

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/stratixv

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_mf

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/220model

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/sgate

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_lnsim

# D:/quartus_16.1/data_transfer/simulation/qsim/work

# Loading altera_ver.dffeas

# Loading sv_std.std

# Loading altera_lnsim_ver.generic_m20k

# Loading altera_lnsim_ver.altera_lnsim_functions

# Loading altera_lnsim_ver.common_28nm_ram_block

# Loading altera_lnsim_ver.common_28nm_ram_register

# Loading altera_lnsim_ver.common_28nm_ram_pulse_generator

# Loading altera_lnsim_ver.generic_28nm_hp_mlab_cell_impl

# Loading altera_lnsim_ver.common_porta_registers

# Loading altera_lnsim_ver.common_28nm_mlab_cell_core

# Loading altera_lnsim_ver.common_28nm_mlab_cell_pulse_generator

# ** Error: (vsim-3033) data_transfer.vo(16260): Instantiation of 'stratixv_hssi_pma_tx_cgb' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /data_transfer_vlg_vec_tst/i1 File: data_transfer.vo

# Searched libraries:

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/stratixv

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_mf

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/220model

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/sgate

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_lnsim

# D:/quartus_16.1/data_transfer/simulation/qsim/work

# ** Error: (vsim-3033) data_transfer.vo(16391): Instantiation of 'stratixv_hssi_pma_tx_ser' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /data_transfer_vlg_vec_tst/i1 File: data_transfer.vo

# Searched libraries:

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/stratixv

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_mf

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/220model

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/sgate

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_lnsim

# D:/quartus_16.1/data_transfer/simulation/qsim/work

# ** Error: (vsim-3033) data_transfer.vo(16464): Instantiation of 'stratixv_hssi_pma_aux' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /data_transfer_vlg_vec_tst/i1 File: data_transfer.vo

# Searched libraries:

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/stratixv

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_mf

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/220model

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/sgate

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_lnsim

# D:/quartus_16.1/data_transfer/simulation/qsim/work

# ** Error: (vsim-3033) data_transfer.vo(16490): Instantiation of 'stratixv_hssi_pma_tx_buf' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /data_transfer_vlg_vec_tst/i1 File: data_transfer.vo

# Searched libraries:

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/stratixv

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_mf

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/220model

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/sgate

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_lnsim

# D:/quartus_16.1/data_transfer/simulation/qsim/work

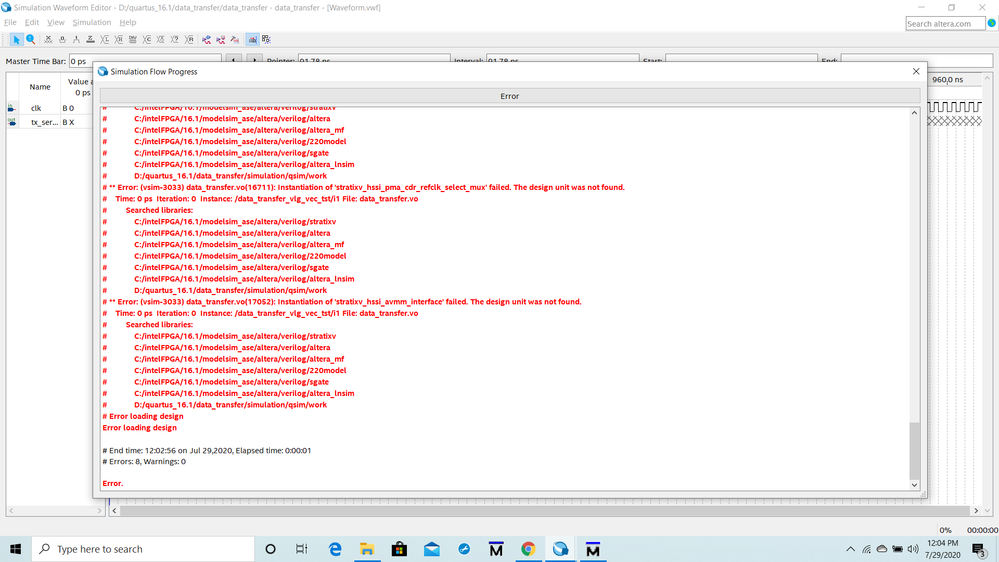

# ** Error: (vsim-3033) data_transfer.vo(16577): Instantiation of 'stratixv_channel_pll' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /data_transfer_vlg_vec_tst/i1 File: data_transfer.vo

# Searched libraries:

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/stratixv

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_mf

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/220model

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/sgate

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_lnsim

# D:/quartus_16.1/data_transfer/simulation/qsim/work

# ** Error: (vsim-3033) data_transfer.vo(16711): Instantiation of 'stratixv_hssi_pma_cdr_refclk_select_mux' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /data_transfer_vlg_vec_tst/i1 File: data_transfer.vo

# Searched libraries:

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/stratixv

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_mf

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/220model

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/sgate

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_lnsim

# D:/quartus_16.1/data_transfer/simulation/qsim/work

# ** Error: (vsim-3033) data_transfer.vo(17052): Instantiation of 'stratixv_hssi_avmm_interface' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /data_transfer_vlg_vec_tst/i1 File: data_transfer.vo

# Searched libraries:

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/stratixv

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_mf

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/220model

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/sgate

# C:/intelFPGA/16.1/modelsim_ase/altera/verilog/altera_lnsim

# D:/quartus_16.1/data_transfer/simulation/qsim/work

# Error loading design

Error loading design

# End time: 12:02:56 on Jul 29,2020, Elapsed time: 0:00:01

# Errors: 8, Warnings: 0

Error.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Based on the errors, it seems that you might be missing some libraries or simulation models.

You will need to check and compile the design files before running the simulation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We do not receive any response from you to the previous question/reply/answer that I have provided. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

Best Regards,

Shyan Yew

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page