- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

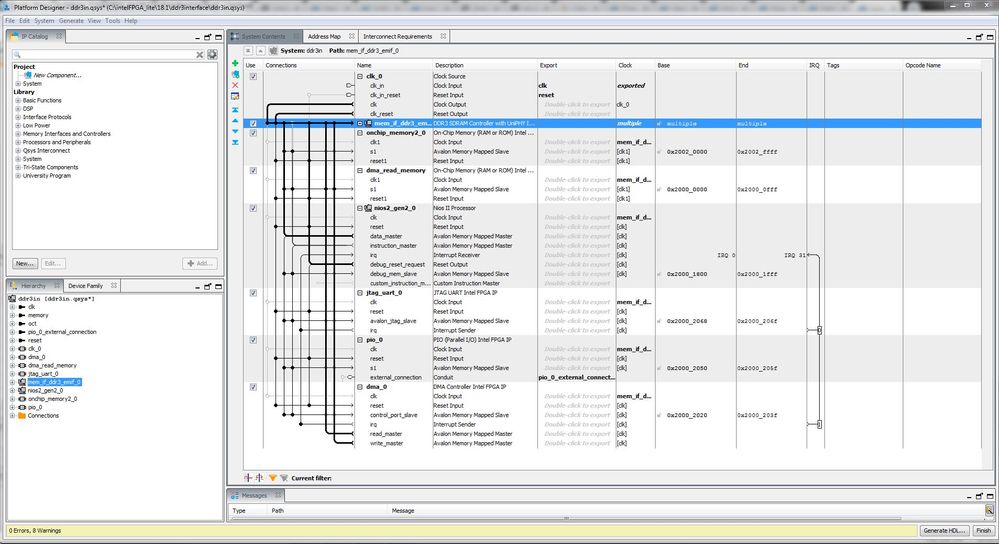

I am trying to design ddr3 interface using Qsys in Quartus Prime Lite Edition for cyclone V GT (5CGTFD9E5F35C7) Development board. While running timing analysis, I am facing setup and hold violations due to negative slack as can be seen below

while searching solution for it came to know that negative slack can be remove by "duplicating the nodes" or "reducing the combinational logic levels in the path of the signal". But nowhere found how to do that. should I change in code or there is some tool to do so.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Those solutions are not typically what you would need to do to solve timing issues in an EMIF IP, only if the timing issues extended into the internal logic of your design. Are you using the hard or soft IP? Go back into the IP Parameter editor and double-check all your settings and timing values. Since you say you are using a dev kit, you should try using the example EMIF design that should be included with the download for the kit. The IP settings in the included design would already be set up correctly for that particular kit.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you .

I am using hard IP. Is that makes difference in parameter setting ??

And I have already checked IP parameters but will check again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As you suggested I tried to find example design for ddr3 and used the IP parameters in my design . I facing following errors (earlier there was no errors):

Error: Quartus Prime Analysis & Synthesis was unsuccessful. 3 errors, 9 warnings

Error: Peak virtual memory: 771 megabytes

Error: Processing ended: Wed Nov 06 17:23:57 2019

Error: Elapsed time: 00:02:29

Error: Total CPU time (on all processors): 00:03:45

The only thing I have changed is ddr3 IP parameters. Please suggest possible solution for it.

Below is Qsys system I have created(and same has been attached):

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The error messages are not informational. Can you browse and see if there is other indications on what went wrong? Look at the 'Flow Messages'

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What do the errors say?

So you're saying from this download (http://fpgadownload.intel.com/outgoing/devkit/13.0/cycloneVGT_5cgtfd9ef35_fpga_v13.0.0.1.zip) you opened the "golden top" project, compiled it, and got synthesis errors? Since the download is for an older version of Quartus, you would probably need to update the IP, but that project should be the starting point.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes I used that download but not compiled "golden top" . Instead I opened "q_sys_hmc.qsys" from "board_test_system" (examples\board_test_system\qts_ddr3\c5gt_ddr3\ ). From there opened ddr3 uniphy IP and made a preset with exactly same parameters and settings.

And further added that preset to my project and compiled it and got synthesis errors. You said that:

"Since the download is for an older version of Quartus, you would probably need to update the IP, but that project should be the starting point."

when I opened the example project I updated the IP, but what you mean by "that project should be the starting point"??

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I mean you should take the example project, make sure it works, then customize it for your own use. Use the project itself as a base. Don't try to copy the settings you see in the example project into your own because you'll inevitably miss something.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, one more thing is to compare your design QSF vs example design QSF. Spot out any setting that potentially cause the timing violation. the slack value is huge, there should be something obvious that cause the violation.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page