Hi,

I was trying to simulate a simple circuit with Quartus, to use the Timing Analyzer for understand how the static timing analysis works.

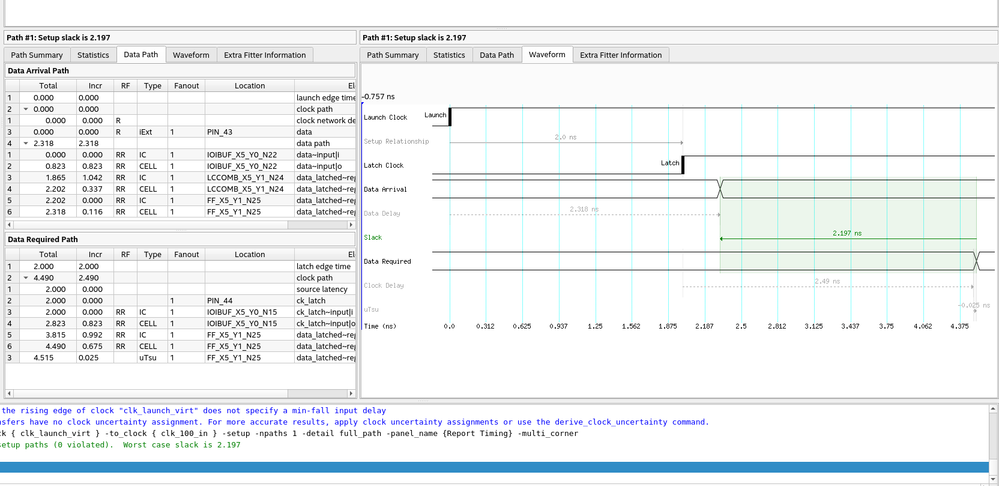

I was wandering if there is a way to disable the optimization of the tool in order to remove the Data Delay and Clock Delay corrections (see the above picture) added by the tool to close the timing.

Thanks in advance for the answer.

Papu

So you're talking about the Optimize Hold Timing setting. Delay is added to meet hold timing at the expense of some setup slack. Assignments menu -> Settings -> Compiler Settings -> Advanced Fitter Settings.

链接已复制

No. Delay is inherent to signals reaching their destination so you cannot remove these delays. I think you're misinterpreting "simulation" here. For a functional simulation to verify the design is working functionally, yes, delays are not taken into account. It just looks at how the logic itself functions (i.e. make sure a 1 ANDed with another signal going high produces a 1).

The idea behind timing analysis to to make sure that a receiving/latch register correctly latches in data, based on the register's setup and hold timing requirements, which is inherent to the silicon. As such, the delays for when the clocks arrive at the launch and latch registers as well as the data delay to get the data from the launch register to the latch register are required for such an analysis.

While more difficult to set up and it takes much longer to run (and it's not supported for every device), a gate-level simulation (in a 3rd party simulation tool) does test functionality and does take data delays into account. Between an RTL functional simulation and timing analysis, you fully verify your design while avoiding having to perform a gate-level sim.

I think I explained myself poorly. I noticed that during compilation quartus has the ability to insert delays on the data and clock lines. I'm not sure how he manages to insert them, but he does it to try to close the timing. If I define via sdc for example "set input delay max/min" assuming that there is an external device that launches the data towards the fpga, quartus appropriately adds delays on the data/clock to be able to latch the data correctly. I was wondering if it was possible to eliminate this correction function..

So you're talking about the Optimize Hold Timing setting. Delay is added to meet hold timing at the expense of some setup slack. Assignments menu -> Settings -> Compiler Settings -> Advanced Fitter Settings.

do you agree that quartus has the ability to add delays to both data and clock? adding delay on the data improves the timing on the hold, does adding delay on the clock improve the timing on the setup?

Am I saying this right?

Optimize hold timing is for data paths only. For clocks, there used to be an option called Beneficial Skew that would intentionally add delay on the latch clock to improve setup slack (data can arrive later and still meet setup time).

I think this was removed at some point (I don't see it in my 23.3 Pro) because it wasn't good to have skew between the launch and latch clocks without user control. If you need skew like that, better to use a second PLL output (much more plentiful in newer devices than they used to be) and add a phase shift which you can set yourself.

my greetings,

Luca.

Hi Luca,

That setting still can be found in Advanced Fitter Settings for Standard version.