- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

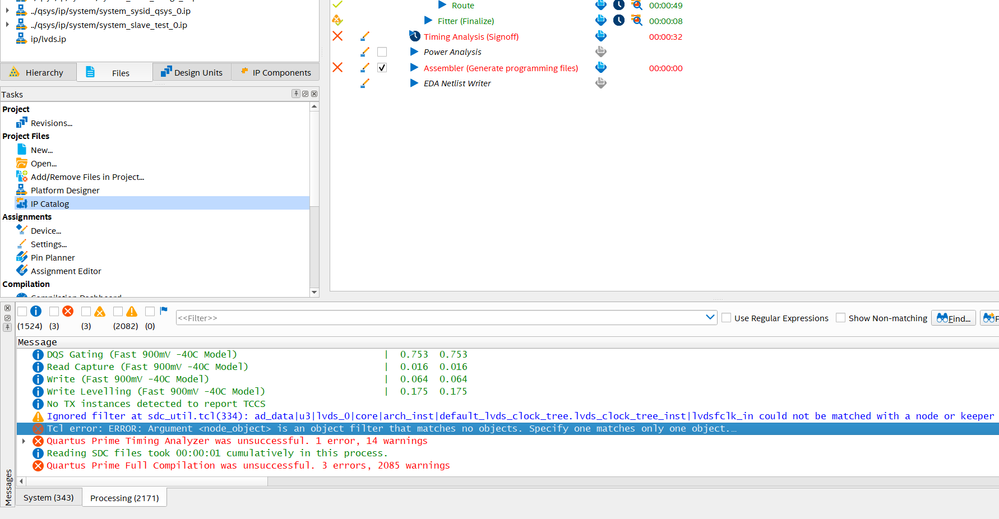

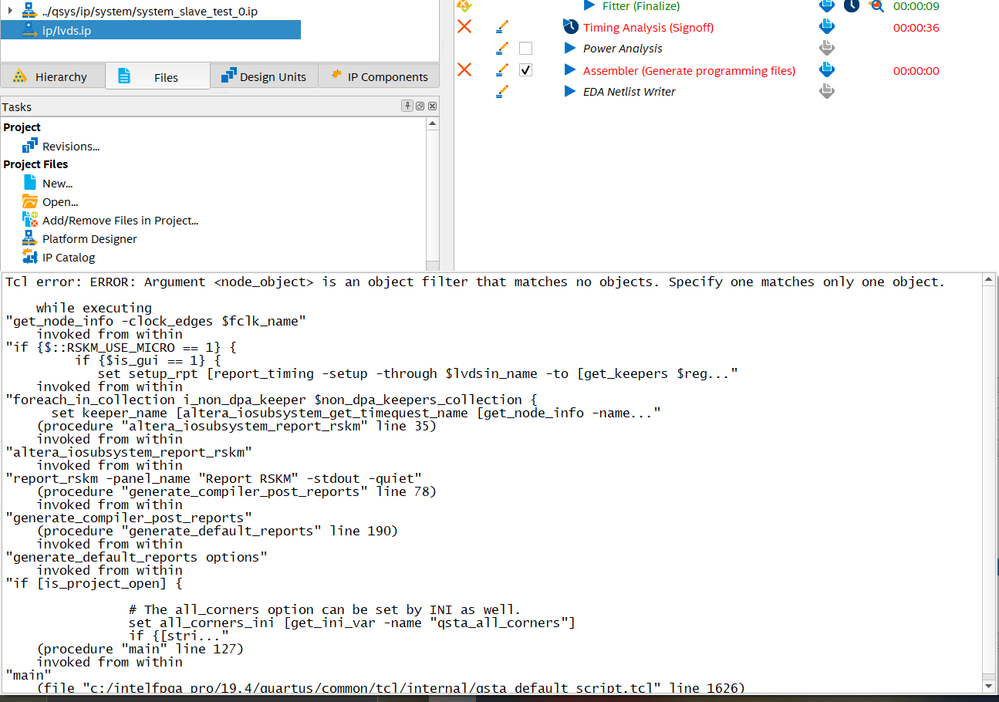

I'm using LVDS SERDES Intel FPGA IP in my project. I use RX Non-DPA. My project compiles almost successfully, except in Timing Analysis. In the end of the Timing Analysis, I got "Tcl error: ERROR: Argument <node_object> is an object filter that matches no objects. Specify one matches only one object.". I attached the image and detail of this error:

My quartus is "Quartus Prime Version 19.4.0 Build 64 12/04/2019 SC Pro Edition".

Thank you,

Yoshitaka

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I request the design for investigation?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Let me apologize for the late reply.

To share the design with you, I have been trying to reproduce this error in a minimal way. Then I somehow fixed the error.

The reason of this problem is caused by an auto-reset logic attached to the SERDES module. The auto-reset logic was implemented in a wrong way, which does not auto-reset the SERDES. I fixed this logic and the project is compiled successfully.

Thank you,

Yoshitaka

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yoshitaka,

It is glad to hear that you found the root cause. Thanks for the reply. I believe your reply is beneficial to other users.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello KhaiY,

we get the same error as described here. We also tried it without the auto-reset port but still we get the same error message. We get the error using version 19.3_pro and 19.4_pro.

The next step was generating an example design using the button within qsys. Creating a quartus project which uses the ed_synth_tx_rx.qsys as top level, we get an similar error. It says "Tcl error: ERROR: Argument <clk_object> is a collection with more than one object. Specify a collection with one object."

The error occurs in line 402 within sdc_util.tcl which is part of altera_lvds_core20. In contrast, the error occurs in line 400 for our design.

Interestingly, creating the same example within quartus 18.0.1, we don't get any error during the timing analyzer step.

Do you have any idea what the problem could be?

Thanks

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael,

Can you provide the design.qar for Pro19.4 for investigation?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello KhaiY,

I cannot find such a file within the project folder. I found some files in the Altera installation folder. However, I don't think they are relevant.

Can you explain how to find or generate this file?

Thanks

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael,

You may generate the .qar file by clicking on Project > Archive Project

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael,

I have filed a case to our developer. I will update once I received the feedback from the team.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi to all,

I have the exact issue (Tcl error: ERROR: Argument <node_object> is an object filter that matches no objects. Specify one matches only one object.) with a design that contains the LVDS SERDES core, in non-DPA mode, during the Timing analyzer phase, running Quartus 19.4.0 Build 64.

The same design works flawlessly in Quartus Pro 19.1.0 Build 240

I tried to clean the project and regenerate the IP cores, but without success. I'm not using Qsys, but the raw IP connected to custom logic. The PLL of LVDS is not external but internal to the SERDES IP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I received the feedback. You may add the below constraint in the sdc file:

derive_pll_clocks -create_base_clocks

or

In the attached design, you can use the SDC generated for the example design, which already contains this SDC function call:

set_global_assignment -name SDC_FILE lvds_0_example_design/lvds_0_example_design_example_design/ed_synth.sdc

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY,

I saw the example design, however I'm already using the option "-create_base_clocks" in the directive "derive_pll_clocks".

I want to remark that the SAME design IS WORKING flawlessly in Quartus Pro 19.1, instead it fails in:

- Quartus pro 19.3

- Quartus pro 19.4

- Quartus pro 20.1

Any idea? I can provide my design if helps, or open a separate topic in the forum.

Regards.

Gabriele

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Gabriele,

Can you create a separate topic and provide the design in the new topic?

In Michael's design, I have tested that the error is fixed by adding the sdc constraint derive_pll_clocks -create_base_clocks

For your design, there might be other root cause and require further investigation.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sure, let me try first to replicate the error with a minimal version of the design, because the project itself is quite large.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sure. Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is the new topic with attached the reduced archived version of the project.

https://forums.intel.com/s/question/0D50P00004eWYpTSAW/tcl-error-in-timing-analysis-phase-using-lvds-serdes-rx-ip

Regards.

Gabriele

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sure. Please allow me some time to look into this in the new forum post.

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

H KhaiY,

sorry for the late reply, we have some license issues on our server at the moment.

However, I have tested your solution locally and it works for the example design.

I did not expect that the sdc file is not part of the project by default. So, I did not checked this.

Adding the example sdc solved the error.

I will apply the same solution to our design now. As the synthesis will require some time, I will give you an update once it is finished.

Thank you.

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael,

May I know if you have any updates?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY,

unfortunately, the error in our design was not solved by this solution. We still get an error in line 400 in the tcl script. However, we have changed our costom hardware during the last months resulting in an update of our design. This also affects the reference clock of the IOPLL for the lvds core. At the moment, I will update the design and check if the error still occurs. Once I get first results, I will give you an update.

Thanks.

Michael

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page