- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

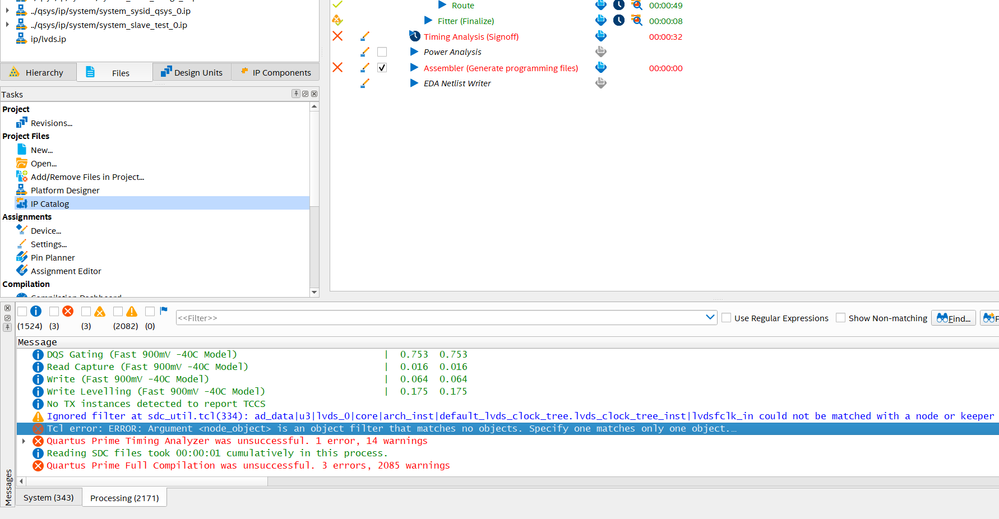

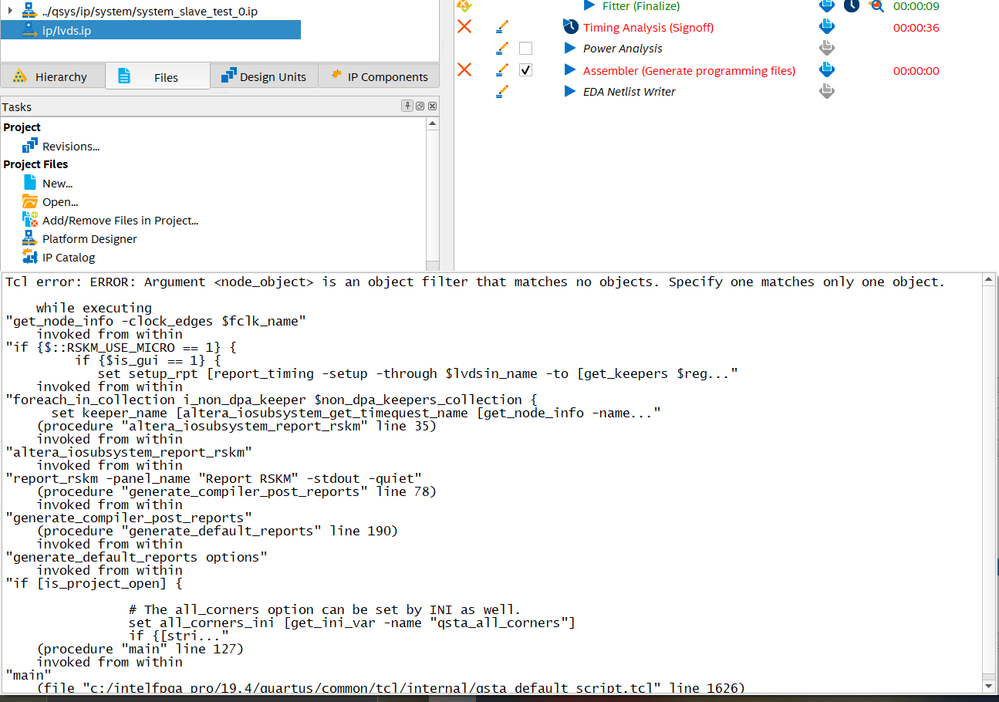

I'm using LVDS SERDES Intel FPGA IP in my project. I use RX Non-DPA. My project compiles almost successfully, except in Timing Analysis. In the end of the Timing Analysis, I got "Tcl error: ERROR: Argument <node_object> is an object filter that matches no objects. Specify one matches only one object.". I attached the image and detail of this error:

My quartus is "Quartus Prime Version 19.4.0 Build 64 12/04/2019 SC Pro Edition".

Thank you,

Yoshitaka

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY,

I discussed the issue with a colleague of mine and I have found something interesting afterwards.

The script sdc_util.tcl located in the synth folder of the altera_lvds_core which is a subfolder of lvds_rx and lvds_tx and the sdc file, lvds_rx_altera_lvds_core20_191_5u346cy.sdc, expect that there is a signal called ..|arch_inst|default_lvds_clock_tree.lvds_clock_tree_inst|lvdsfclk_in within the lvds rx instance. However, I can see, for instance, in the technology map viewer that the instance, lvds_clock_tree_inst, is only part of the lvds_tx core and the lvds_rx instance only uses the lvdsfclk_out signal. In other words, the lvds_rx has no lvds_clock_tree_inst. We can see this fact in the list of atoms in the technology map viewer as well. Hence, there exists no node called ...|lvds_rx|lvds_0|core|arch_inst|default_lvds_clock_tree.lvds_clock_tree_inst|lvdsfclk_in, which is the node causing the error.

Setting lvds_clock_tree_inst_name within lvds_rx_altera_lvds_core20_191_5u346cy.sdc removed some warnings. However, the sdc_util.tcl is very generic and the part regarding lvds_rx is also executed in the sdc_util.tcl of the lvds_tx. Therefore, I was not able to assign fclk_name to the correct location, since this would break other iterations of the loop starting in line 334. Moreover, this would not be the correct way anyway, since these are auto-generated scripts.

Do you have any solution for us to assign the correct location of the lvds_clock_tree_inst for the lvds_rx instance?

Thank you.

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael,

May I confirm that the sdc constraint derive_pll_clocks -create_base_clocks solves the initial error (Line 1626)?

For the second error (Line 400), could you open a new forum post so that we can continue the discussion in the new post? This is to avoid confusion to the other user on the error and solution.

For example, Gabriele's error (Line 1613) has different solution and it is tracked in another post: https://forums.intel.com/s/question/0D50P00004eWYpTSAW/tcl-error-in-timing-analysis-phase-using-lvds-serdes-rx-ip

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY,

it solves not the initial error mentioned in the thread, which YTagu5 has opened. It solves the minimal working design which I thought is similar to our problem. It wasn't the same root cause than in our design. The minimal working design is just the example design which can be created in the platform designer for lvds cores. For this example, the solution with derive_pll_clocks -create_base_clocks works.

However, the solution in Gabriele's post also solved our issue. I put the solution there to the sdc_util.tcl files in both cores, lvds_rx and lvds_tx.

Sorry, I didn't check his thread further, since it sounded for me like a different error due to your suggestion to create a new thread.

I will also check if the solution in Gabriele's thread will remove the warnings caused by the file lvds_rx_altera_lvds_core20_191_5u346cy.sdc. I will write my findings in his thread.

Thank you.

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Michael,

Sure. Thanks for the update.

Thanks.

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »