- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Quartus Support/Expert,

I guess this is a very entry level question. I hope some experienced user can answer easily.

I have a TI dev kit, which is in STD version 14, and the device is 10AX115H2F34E1SG, it compiles and no slack at Standard version 18.1

now I update to 10AX115S2F45I1SG( Intel AX PCIe dev kit). and using PRO 21.3.

after I compile I got a lot slack, like this

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|jesd_clk_rst_gen_0|JESD_A10_PLL.jesd_pll_inst|iopll_0|outclk2 -12.442 -42084.050 7473 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|jesd_clk_rst_gen_0|JESD_A10_PLL.jesd_pll_inst|iopll_0|outclk1 -12.239 -23247.369 3544 Slow 900mV 100C Model

jesd204b_inst|emif_0|emif_0_core_usr_clk -1.705 -121.013 75 Fast 900mV 100C Model

clkintopb_p -1.549 -152.384 122 Fast 900mV 100C Model

fx3_clk_iopll_inst|iopll_0|outclk0 -0.885 -13.901 29 Slow 900mV -40C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i1_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[0]|tx_coreclkin -0.388 -0.388 1 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i0_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[0]|tx_coreclkin -0.286 -0.286 1 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i2_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[2]|tx_coreclkin -0.250 -0.250 1 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i0_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[3]|tx_coreclkin -0.246 -0.246 1 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i1_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[3]|tx_coreclkin -0.219 -0.219 1 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i2_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[0]|tx_coreclkin -0.185 -0.185 1 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i0_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[2]|tx_coreclkin -0.179 -0.179 1 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i1_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[2]|tx_coreclkin -0.175 -0.175 1 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i0_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[1]|tx_coreclkin -0.133 -0.133 1 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i1_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[1]|tx_coreclkin -0.118 -0.118 1 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i2_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[1]|tx_coreclkin -0.117 -0.117 1 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i2_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[3]|tx_coreclkin -0.105 -0.105 1 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i3_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[1]|tx_coreclkin 0.195 0.000 0 Slow 900mV 100C Model

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|JESD_TX.u_jesd_top_tx|jesd_enc_xcvr_0|TX_XCVR.i3_xcvr_jesd_tx|jesd204_0|g_xcvr_native_insts[0]|tx_coreclkin 0.221 0.000 0 Slow 900mV 100C Model

while I am watching the Intel training video clips, and reading Using the Intel Quartus Prime Timing Analyzer.

I hope get got some help from the methodology level, if there is a clock has thousands end points failed slack analysis. where to start to solve this problem.

Sincerely.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sstrel,

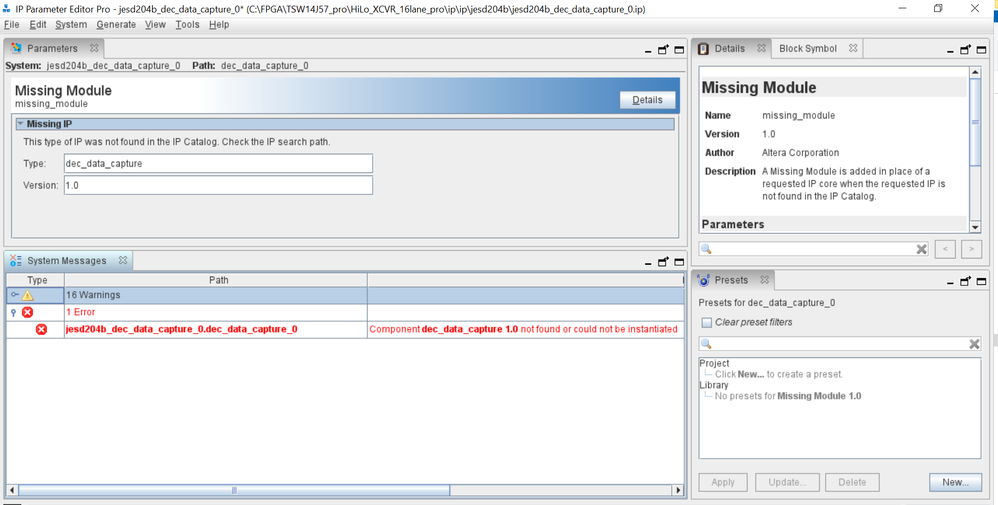

If I manually open one of the IP in the list. it will fail because "component dec_data_capture 1.0 not found or could not be instantiated".

I confirmed the file is there in the first line listed directory. I don't know why it couldn't be instantiated.

but the overall project can compile without any problem.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Since you are using Q21.3 Pro, I'd say look at Design Assistant report and Fast Forward Compile report. These reports are useful in detecting location of the black hole and critical chain respectively.

Design Assistant: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qpp-design-recommendations.pdf#page=93

Fast forward compile: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qpp-compiler.pdf#page=30

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I just noticed most of them are from IP modules, did you re-generate the IP? Did you update them?

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nurina,

for standard version, there is a reminder to automatic or manually update the IP. for the Pro version, I didn't see any signs of over time IP or module.

I am new to platform designer, even I have gone through the training video and some part of the manual, I am still not quit confident that I did it correctly.

when you say update them, do I need to pick some of them one by one, or there is a click for all button. how do I know all the IPs are update to date?

Thank you very much for the following up post.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If all the IP are in Platform Designer, you can just regenerate the system there or select Upgrade IP Cores from the System menu if it's available.

If the IP are not in a PD system, you can do the same from Quartus: Project menu -> Upgrade IP Components.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sstrell,

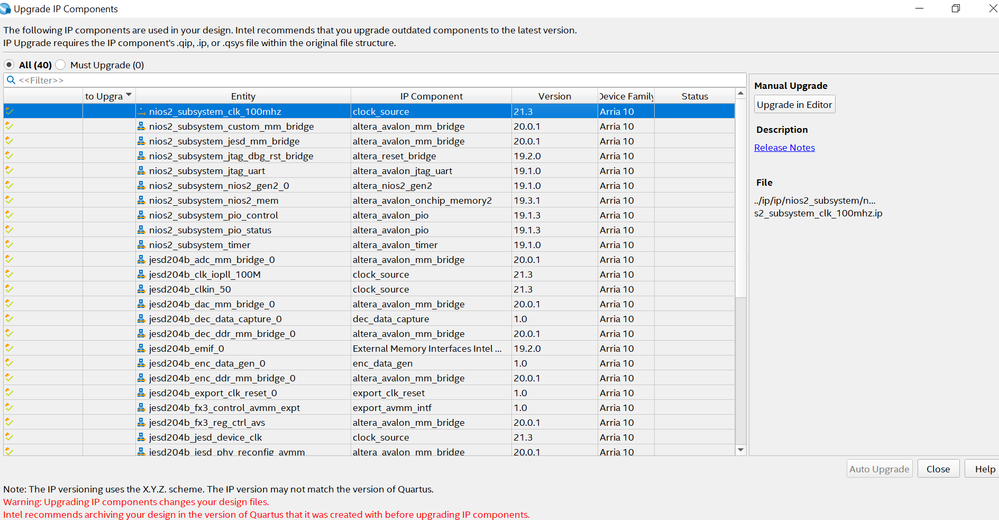

I posted the Quartus IP upgrade page.

it says All (40) IPs. there are none of them Must upgrade.

and in the list, the versions are different. some of them for example is 21.3, some are 19.1.0. should I manually upgrade all none 21.3 version IP to the latest?

Thanks for help

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sstrel,

If I manually open one of the IP in the list. it will fail because "component dec_data_capture 1.0 not found or could not be instantiated".

I confirmed the file is there in the first line listed directory. I don't know why it couldn't be instantiated.

but the overall project can compile without any problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Intel Experts and Friends,

I am still try to figure out how to fix/reduce the timing issue, because the 18.1 standard version don't have these problem, so the PRO version should not have that much timing failures. I guess there was something wrong while I am upgrade to the Quartus Pro.

but there were not much operation when did the upgrade, just made few clicks, then everything seems OK except the timing analysis.

if I couldn't figure out the upgrade procedure problems, for the regular failure like this, where should I start to trouble shooting.

thank you very much,

David

jesd204b_inst|jesd_top_qsys_0|jesd_top_qsys_0|u_jesd_top_inst|jesd_clk_rst_gen_0|JESD_A10_PLL.jesd_pll_inst|iopll_0|outclk2 -12.442 -42084.050 7473 Slow 900mV 100C Model

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

What steps did you take to migrate from std to pro? You need to make changes to your qsf file, sdc and tcl scripts and maybe even RTL code for a successful migration. Refer to this video training on migrating to the Intel Quartus Prime Pro: https://www.youtube.com/watch?v=P_6gemOLtjE

Even though your timing has closed in Standard edition, it might fail in Pro edition. This is because the timing algorithm is different, so you may have to take different/more steps to close timing with the same project. The same applies to when you migrate to a different version of Quartus.

Regards,

Nurina

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We did not receive any response to the previous question/reply/answer that I have provided, thus I will put this case to close pending. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

Regards,

Nurina

P/S: If you like my comment, feel free to give Kudos. If my comment solved your problem, feel free to accept my comment as solution!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page