- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to run Linux on aria10 device but boot got stuck on the line Waiting for root device /dev/mmcblk0p2…

here is the content of putty

U-Boot 2014.10 (May 20 2021 - 17:06:24)

CPU : Altera SOCFPGA Arria 10 Platform

BOARD : Altera SOCFPGA Arria 10 Dev Kit

I2C: ready

DRAM: WARNING: Caches not enabled

SOCFPGA DWMMC: 0

FPGA: writing socfpga.rbf ...

Full Configuration Succeeded.

DDRCAL: Success

INFO : Skip relocation as SDRAM is non secure memory

Reserving 2048 Bytes for IRQ stack at: ffe386e8

DRAM : 1 GiB

WARNING: Caches not enabled

MMC: In: serial

Out: serial

Err: serial

Model: SOCFPGA Arria10 Dev Kit

Net: dwmac.ff800000

Hit any key to stop autoboot: 0

FPGA must be in Early Release mode to program core.

fpga - loadable FPGA image support

** Unable to read file u-boot.scr **

5450416 bytes read in 256 ms (20.3 MiB/s)

20080 bytes read in 5 ms (3.8 MiB/s)

FPGA BRIDGES: enable

Kernel image @ 0x008000 [ 0x000000 - 0x532ab0 ]

## Flattened Device Tree blob at 00000100

Booting using the fdt blob at 0x000100

Loading Device Tree to 01ff8000, end 01fffe6f ... OK

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 5.10.0-66217-gea6585a048f5 (root@risclab-VirtualBox) (arm-linux-gnueabihf-gcc (Linaro GCC 7.2-2017.11) 7.2.1 20171011, GNU ld (Linaro_Binutils-2017.11) 2.28.2.20170706) #1 SMP Thu May 20 12:31:53 PKT 2021

[ 0.000000] CPU: ARMv7 Processor [414fc091] revision 1 (ARMv7), cr=10c5387d

[ 0.000000] CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

[ 0.000000] OF: fdt: Machine model: ALTR,a10s_ghrd

[ 0.000000] Memory policy: Data cache writealloc

[ 0.000000] Zone ranges:

[ 0.000000] Normal [mem 0x0000000000000000-0x000000002fffffff]

[ 0.000000] HighMem [mem 0x0000000030000000-0x000000003fffffff]

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000000000000-0x000000003fffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000000000000-0x000000003fffffff]

[ 0.000000] percpu: Embedded 19 pages/cpu s45132 r8192 d24500 u77824

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 260608

[ 0.000000] Kernel command line: console=ttyS0,115200 root=/dev/mmcblk0p2 rw rootwait

[ 0.000000] Dentry cache hash table entries: 131072 (order: 7, 524288 bytes, linear)

[ 0.000000] Inode-cache hash table entries: 65536 (order: 6, 262144 bytes, linear)

[ 0.000000] mem auto-init: stack:off, heap alloc:off, heap free:off

[ 0.000000] Memory: 1026132K/1048576K available (9216K kernel code, 748K rwdata, 1820K rodata, 1024K init, 176K bss, 22444K reserved, 0K cma-reserved, 262144K highmem)

[ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1

[ 0.000000] ftrace: allocating 29782 entries in 59 pages

[ 0.000000] ftrace: allocated 59 pages with 5 groups

[ 0.000000] rcu: Hierarchical RCU implementation.

[ 0.000000] rcu: RCU event tracing is enabled.

[ 0.000000] Rude variant of Tasks RCU enabled.

[ 0.000000] rcu: RCU calculated value of scheduler-enlistment delay is 10 jiffies.

[ 0.000000] NR_IRQS: 16, nr_irqs: 16, preallocated irqs: 16

[ 0.000000] L2C: device tree omits to specify unified cache

[ 0.000000] L2C-310 erratum 769419 enabled

[ 0.000000] L2C-310 enabling early BRESP for Cortex-A9

[ 0.000000] L2C-310: enabling full line of zeros but not enabled in Cortex-A9

[ 0.000000] L2C-310 ID prefetch enabled, offset 1 lines

[ 0.000000] L2C-310 dynamic clock gating enabled, standby mode enabled

[ 0.000000] L2C-310 cache controller enabled, 8 ways, 512 kB

[ 0.000000] L2C-310: CACHE_ID 0x410030c9, AUX_CTRL 0x76460001

[ 0.000000] random: get_random_bytes called from start_kernel+0x3a0/0x548 with crng_init=0

[ 0.000000] GIC: PPI13 is secure or misconfigured

[ 0.000000] GIC: PPI13 is secure or misconfigured

[ 0.000000] clocksource: timer: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 38225208935 ns

[ 0.000005] sched_clock: 32 bits at 50MHz, resolution 20ns, wraps every 42949672950ns

[ 0.000014] Switching to timer-based delay loop, resolution 20ns

[ 0.000324] Console: colour dummy device 80x30

[ 0.000356] Calibrating delay loop (skipped), value calculated using timer frequency.. 100.00 BogoMIPS (lpj=500000)

[ 0.000371] pid_max: default: 32768 minimum: 301

[ 0.000488] Mount-cache hash table entries: 2048 (order: 1, 8192 bytes, linear)

[ 0.000500] Mountpoint-cache hash table entries: 2048 (order: 1, 8192 bytes, linear)

[ 0.001062] CPU: Testing write buffer coherency: ok

[ 0.001092] CPU0: Spectre v2: using BPIALL workaround

[ 0.001259] CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

[ 0.001634] Setting up static identity map for 0x100000 - 0x100060

[ 0.001751] rcu: Hierarchical SRCU implementation.

[ 0.002003] smp: Bringing up secondary CPUs ...

[ 0.002364] smp: Brought up 1 node, 1 CPU

[ 0.002376] SMP: Total of 1 processors activated (100.00 BogoMIPS).

[ 0.002384] CPU: All CPU(s) started in SVC mode.

[ 0.002824] devtmpfs: initialized

[ 0.005933] VFP support v0.3: implementor 41 architecture 3 part 30 variant 9 rev 4

[ 0.006220] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

[ 0.006241] futex hash table entries: 512 (order: 3, 32768 bytes, linear)

[ 0.006955] NET: Registered protocol family 16

[ 0.007621] DMA: preallocated 256 KiB pool for atomic coherent allocations

[ 0.008446] hw-breakpoint: found 5 (+1 reserved) breakpoint and 1 watchpoint registers.

[ 0.008457] hw-breakpoint: maximum watchpoint size is 4 bytes.

[ 0.013885] OF: /sopc@0/gpio@0xffc02900/gpio-controller@0: could not get #gpio-cells for /sopc@0/clkmgr@0xffd04000/clock_tree/l4_sp_clk

[ 0.013961] OF: /sopc@0/gpio@0xffc02a00/gpio-controller@0: could not get #gpio-cells for /sopc@0/clkmgr@0xffd04000/clock_tree/l4_sp_clk

[ 0.014030] OF: /sopc@0/gpio@0xffc02b00/gpio-controller@0: could not get #gpio-cells for /sopc@0/clkmgr@0xffd04000/clock_tree/l4_mp_clk

[ 0.015495] OF: /sopc@0/gpio@0xffc02900/gpio-controller@0: could not get #gpio-cells for /sopc@0/clkmgr@0xffd04000/clock_tree/l4_sp_clk

[ 0.015564] OF: /sopc@0/gpio@0xffc02a00/gpio-controller@0: could not get #gpio-cells for /sopc@0/clkmgr@0xffd04000/clock_tree/l4_sp_clk

[ 0.015631] OF: /sopc@0/gpio@0xffc02b00/gpio-controller@0: could not get #gpio-cells for /sopc@0/clkmgr@0xffd04000/clock_tree/l4_mp_clk

[ 0.023245] vgaarb: loaded

[ 0.023434] SCSI subsystem initialized

[ 0.023595] usbcore: registered new interface driver usbfs

[ 0.023630] usbcore: registered new interface driver hub

[ 0.023680] usbcore: registered new device driver usb

[ 0.024212] pps_core: LinuxPPS API ver. 1 registered

[ 0.024223] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

[ 0.024238] PTP clock support registered

[ 0.024376] FPGA manager framework

[ 0.025194] clocksource: Switched to clocksource timer

[ 0.629499] NET: Registered protocol family 2

[ 0.629967] tcp_listen_portaddr_hash hash table entries: 512 (order: 0, 6144 bytes, linear)

[ 0.629993] TCP established hash table entries: 8192 (order: 3, 32768 bytes, linear)

[ 0.630056] TCP bind hash table entries: 8192 (order: 4, 65536 bytes, linear)

[ 0.630158] TCP: Hash tables configured (established 8192 bind 8192)

[ 0.630266] UDP hash table entries: 512 (order: 2, 16384 bytes, linear)

[ 0.630313] UDP-Lite hash table entries: 512 (order: 2, 16384 bytes, linear)

[ 0.630493] NET: Registered protocol family 1

[ 0.630936] RPC: Registered named UNIX socket transport module.

[ 0.630948] RPC: Registered udp transport module.

[ 0.630954] RPC: Registered tcp transport module.

[ 0.630960] RPC: Registered tcp NFSv4.1 backchannel transport module.

[ 0.630972] PCI: CLS 0 bytes, default 64

[ 0.632140] workingset: timestamp_bits=30 max_order=18 bucket_order=0

[ 0.637157] NFS: Registering the id_resolver key type

[ 0.637187] Key type id_resolver registered

[ 0.637195] Key type id_legacy registered

[ 0.637208] Installing knfsd (copyright (C) 1996 okir@monad.swb.de).

[ 0.637718] ntfs: driver 2.1.32 [Flags: R/W].

[ 0.637874] jffs2: version 2.2. (NAND) © 2001-2006 Red Hat, Inc.

[ 0.638392] bounce: pool size: 64 pages

[ 0.638408] io scheduler mq-deadline registered

[ 0.638415] io scheduler kyber registered

[ 0.641543] dma-pl330 ffda1000.dma: Loaded driver for PL330 DMAC-341330

[ 0.641560] dma-pl330 ffda1000.dma: DBUFF-512x8bytes Num_Chans-8 Num_Peri-32 Num_Events-8

[ 0.643955] Serial: 8250/16550 driver, 2 ports, IRQ sharing disabled

[ 0.644806] printk: console [ttyS0] disabled

[ 0.644870] ffc02100.serial: ttyS0 at MMIO 0xffc02100 (irq = 39, base_baud = 3125000) is a 16550A

[ 1.329894] printk: console [ttyS0] enabled

[ 1.335459] brd: module loaded

[ 1.344600] loop: module loaded

[ 1.348847] libphy: Fixed MDIO Bus: probed

[ 1.353405] CAN device driver interface

[ 1.357530] socfpga-dwmac ff800000.ethernet: IRQ eth_wake_irq not found

[ 1.364121] socfpga-dwmac ff800000.ethernet: IRQ eth_lpi not found

[ 1.370410] socfpga-dwmac ff800000.ethernet: PTP uses main clock

[ 1.376414] socfpga-dwmac ff800000.ethernet: no reset control found

[ 1.382657] socfpga-dwmac ff800000.ethernet: No sysmgr-syscon node found

[ 1.389339] socfpga-dwmac ff800000.ethernet: Unable to parse OF data

[ 1.395955] stmmaceth ff800000.ethernet: IRQ eth_wake_irq not found

[ 1.402199] stmmaceth ff800000.ethernet: IRQ eth_lpi not found

[ 1.408113] stmmaceth ff800000.ethernet: PTP uses main clock

[ 1.413750] stmmaceth ff800000.ethernet: no reset control found

[ 1.419844] stmmaceth ff800000.ethernet: User ID: 0x10, Synopsys ID: 0x37

[ 1.426633] stmmaceth ff800000.ethernet: DWMAC1000

[ 1.431492] stmmaceth ff800000.ethernet: DMA HW capability register supported

[ 1.438605] stmmaceth ff800000.ethernet: RX Checksum Offload Engine supported

[ 1.445717] stmmaceth ff800000.ethernet: COE Type 2

[ 1.450573] stmmaceth ff800000.ethernet: TX Checksum insertion supported

[ 1.457252] stmmaceth ff800000.ethernet: Enhanced/Alternate descriptors

[ 1.463835] stmmaceth ff800000.ethernet: Enabled extended descriptors

[ 1.470254] stmmaceth ff800000.ethernet: Ring mode enabled

[ 1.475722] stmmaceth ff800000.ethernet: Enable RX Mitigation via HW Watchdog Timer

[ 1.483345] stmmaceth ff800000.ethernet: device MAC address 04:ec:3f:ef:ef:d0

[ 1.498125] libphy: stmmac: probed

[ 1.501530] mdio_bus stmmac-0:03: attached PHY driver [unbound] (mii_bus:phy_addr=stmmac-0:03, irq=POLL)

[ 1.512143] dwc2 ffb00000.usb: supply vusb_d not found, using dummy regulator

[ 1.519432] dwc2 ffb00000.usb: supply vusb_a not found, using dummy regulator

[ 1.526807] dwc2 ffb00000.usb: EPs: 16, dedicated fifos, 8064 entries in SPRAM

[ 1.534269] dwc2 ffb00000.usb: DWC OTG Controller

[ 1.539027] dwc2 ffb00000.usb: new USB bus registered, assigned bus number 1

[ 1.546086] dwc2 ffb00000.usb: irq 43, io mem 0xffb00000

[ 1.551969] hub 1-0:1.0: USB hub found

[ 1.555777] hub 1-0:1.0: 1 port detected

[ 1.560373] usbcore: registered new interface driver usb-storage

[ 1.566576] i2c /dev entries driver

[ 1.571214] Synopsys Designware Multimedia Card Interface Driver

[ 1.577529] ledtrig-cpu: registered to indicate activity on CPUs

[ 1.583629] usbcore: registered new interface driver usbhid

[ 1.589202] usbhid: USB HID core driver

[ 1.593240] socfpga_a10_fpga_manager ffd03000.fpgamgr: no clock specified

[ 1.600040] dw_mmc ff808000.flash: IDMAC supports 32-bit address mode.

[ 1.606576] dw_mmc ff808000.flash: Using internal DMA controller.

[ 1.612647] dw_mmc ff808000.flash: Version ID is 270a

[ 1.617721] dw_mmc ff808000.flash: DW MMC controller at irq 42,32 bit host data width,1024 deep fifo

[ 1.627122] socfpga_a10_fpga_manager: probe of ffd03000.fpgamgr failed with error -2

[ 1.635651] NET: Registered protocol family 10

[ 1.640554] mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 400000Hz, actual 396825HZ div = 63)

[ 1.650346] Segment Routing with IPv6

[ 1.654050] sit: IPv6, IPv4 and MPLS over IPv4 tunneling driver

[ 1.660440] NET: Registered protocol family 17

[ 1.664905] NET: Registered protocol family 15

[ 1.669354] can: controller area network core

[ 1.673737] NET: Registered protocol family 29

[ 1.678177] can: raw protocol

[ 1.681132] can: broadcast manager protocol

[ 1.685310] can: netlink gateway - max_hops=1

[ 1.689779] 8021q: 802.1Q VLAN Support v1.8

[ 1.693980] Key type dns_resolver registered

[ 1.698446] oprofile: no performance counters

[ 1.702875] oprofile: using timer interrupt.

[ 1.707223] ThumbEE CPU extension supported.

[ 1.711480] Registering SWP/SWPB emulation handler

[ 1.719419] of_cfs_init

[ 1.721958] of_cfs_init: OK

[ 1.725113] dw-apb-uart ffc02100.serial: forbid DMA for kernel console

[ 1.731823] Waiting for root device /dev/mmcblk0p2...

any help would be appreciated.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know how did you compile your Linux ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have compile lnux kernal version 5.10 from

git source https://github.com/altera-opensource/linux-socfpga.

I have used gcc-linaro as cross compiler .

COMPILER_FILE="gcc-linaro-7.2.1-2017.11-x86_64_arm-linux-gnueabihf"

COMPILER_URL="https://releases.linaro.org/components/toolchain/binaries/7.2-2017.11/arm-linux-gnueabihf/${COMPILER_FILE}.tar.xz"

Commands used to compile

1. make socfpga_defconfig (inside git repository )

2. make zImage

I have basically followed the instruction from https://github.com/tmarkettos/arria10-ubuntu-sdcard to build the sdcard.img image.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also, I have used ari10ghrd as hardware design given in in Demonstration folder of board system cd present on www.han.terasic.com/cd .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The Uboot version is really old, I recommend that you use the new flow below:

https://rocketboards.org/foswiki/Documentation/BuildingBootloader#Arria_10_SoC_45_Boot_from_SD_Card

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @EBERLAZARE_I_Intel ,

Thank you for the reply.

I have followed the flow and now linux is running on HPS. But the hps2fpga bridges are not enabled. I have check /sys/class/fpga_bridges directory and it is empty.

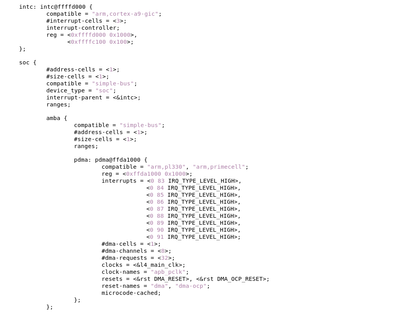

I think since the .dtb file (from linux source) we have, is a bare minimum device tree file and it explain only the harden device connected to hps, so it doesn't describe the soft IPs connected to hps over hps2fpga bridge or lwhps2fpga bridge. screen shot of soc node defined in dtsi file for arria10 in linux source is attached here. It shows that HPS_FPGA bridges are not defined.

Actually, I am trying to integrated open source NVIDIA's Deep Learning Accelerator (NVDLA) with hps. soft IP of NVDLA is connected to hps in platform designer via lwhps2fpga bridge as show in the screen shot attached here.

After device tree is create for this custom project, I need to build nvdla Kernel Module Driver (KMD) with Linux source code, before compiling linux kernel into compressed image (zImage). This kmd is also using a reseved memory region of 1 GB for running NVDLA jobs.

So in conclusion I have three main issues I need help with.

1. Creating device Device driver for any custom project.

I have tried to follow a tutorial given on rocketboard.org for creating device using sopc2dtc command and board.xml files. I have contacted Terasic for board xml files for HAN Pilot Platform but they told me that they don't have xml files for Han. Still I tried using xml files of arria10 SOCkit but it didn't work.

2. editing final device tree file to add node for reserved memory.

3. How build KMD with linux kernel source code.

I have also uploaded the above screen shots as attachment with this comment for your reference.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

1. The xml files should be used from your project which is generated by Quartus, it is located in the "hps_isw_handoff" folder.

2. & 3. Since this is a third party IP, we recommend that you seek the provider of the IP for Linux device tree build and configuration.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I know this topic is quite old but I am just facing the same error (same hardware and ghrd) that my boot process got stuck on the line Waiting for root device /dev/mmcblk0p2…

As proposed I am using the xml files located in the hps_isw_handoff folder to generate the device tree with the following command:

sopc2dts --input a10s_ghrd.sopcinfo --output socfpga_arria10_socdk_sdmmc.dts --type dts --board hps_isw_handoff/hps.xml --board hps_isw_handoff/emif.xml --bridge-removal all --clocks

I guess that those two .xml files are wrong or not enough to generate a functional device tree. Do you have any idea what the problem is?

When I use a precompiled example .dtb the system boots successfully.

Also I am wondering why Terasic claims that they don't have board files since they provide example designs where those files are essential?

Thanks in advance!

Best regards,

Dennis

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page