- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I am running Ubuntu (kernel 4.5) provided by Terasic on my DE1-SoC board.

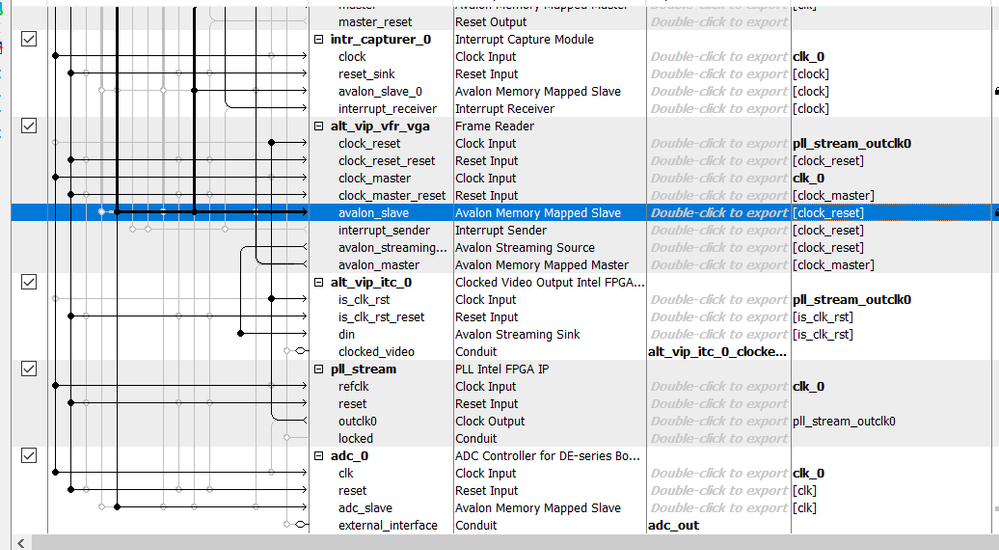

From the demonstrations in the CD, I modified the hardware project and added ADC controller for DE series boards to the Qsys project like this:

The ADC is mapped to 0x0000_0000 to 0x0000_001F as a lightweight HPS to FPGA memory mapped slave.

I generated the HDL, added ADC to the top-level verilog file like this:

https://github.com/giorgi3092/ECG_HW_SW_DE1_SoC/blob/master/DE1_SOC_Linux_FB_HW/DE1_SOC_Linux_FB.v

Compiled the project, converted the .sof file to .rbf file and replaced the existing .rbf file on the SD card with the one I generated (with the same name of course).

I started the DE1-SoC board and it booted normally.

Next, I write the following program to read the values from ADC and print the values on the console:

I map the ADC's base address to the virtual space, then I initiate an update of the 8 channels by writing to the UPDATE register, as described in the IP's manual: ftp://ftp.intel.com/Pub/fpgaup/pub/Intel_Material/18.1/University_Program_IP_Cores/Input_Output/ADC_Controller_for_DE_Series_Boards.pdf chapter 4, software programming model.

I also isolate the 12 bits from 32-bit values.

Then I read the values expecting to read the values of the ADC.

(I slightly modified the code for better illustration of what I am doing (removed extra computations). I don't have the board with me to check if it compiles but you get the idea)..

Running this program, I only get 0's for all 8 channels. If I write any value to the UPDATE register, I read out the exact same value for the UPDATE register. I tried the auto-update register as well, getting the same values.

Maybe my programming model is wrong. Can you give me any feedback?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

anyone? I could not find information about ADC control from HPS running Linux anywhere. I seem to be doing it correctly according to the ADC IP docs but apparently not.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

I apologize for the late response, may I k now which Quartus/SoC EDS version that you used to test this?

I could not access the github page that you shared. Was there any error in Platform Designer/Quartus during compilation?

Also, during booting was there any error or hung up in the booting logs?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you have any follow up from your side?

Regards.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page