- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hardware: DE10-Nano demo board (Cyclone V)

IDE: Arm DS 2022.0

SoC EDS: 20.1 (Standard)

I'm developing a bare metal application for a Cyclone V. I am able to debug directly with no problems when using an on-chip RAM scatter file but I am having issues debugging from SDRAM. Using an SDRAM scatter file, I can debug without issue after first executing U-Boot from the factory SD card image. However, when I try the same with U-Boot built from the latest U-Boot release (2022.04), U-Boot reports an 'undefined instruction' and the processor resets when I begin debugging. Prior to the reset, U-Boot seems to function normally and I am able to execute commands from the terminal window. For reference, the DE10-Nano factory image uses U-Boot 2017.03-rc2.

I understand that the U-Boot build flow changed quite recently. My hunch is that something "under-the-hood" changed along this time that is causing my build of U-Boot to behave differently. The results are the same whether I use the DE10-Nano specific build config "socfpga_cyclone5_de10_nano" or the Cyclone V default build config "socfpga_cyclone5_defconfig" (the latter with DE10-Nano specific handoff data).

Here is a boot log from when I attempt to debug my bare-metal application after executing my build of the current release of U-Boot:

U-Boot SPL 2022.04-21230-gfcf317324c (Oct 14 2022 - 17:52:23 -0500)

U-Boot 2022.04-21230-gfcf317324c (Oct 14 2022 - 17:52:23 -0500)

CPU: Altera SoCFPGA Platform

FPGA: Altera Cyclone V, SE/A6 or SX/C6 or ST/D6, version 0x0

BOOT: SD/MMC Internal Transceiver (3.0V)

Watchdog enabled

DRAM: 1 GiB

Core: 21 devices, 12 uclasses, devicetree: separate

MMC: dwmmc0@ff704000: 0

Loading Environment from MMC... *** Warning - bad CRC, using default environment

In: serial

Out: serial

Err: serial

Model: Terasic DE10-Nano

Net:

Error: ethernet@ff702000 address not set.

No ethernet found.

=> undefined instruction

pc : [<02000bae>] lr : [<0200005f>]

reloc pc : [<c307ebee>] lr : [<c307e09f>]

sp : 03ffffe8 ip : 3ffe5e08 fp : 02000bf8

r10: 02000bf8 r9 : 3bf7fed0 r8 : 00000000

r7 : 02000be7 r6 : 00000000 r5 : 00000000 r4 : 00000000

r3 : 00000000 r2 : 80000000 r1 : 02000d60 r0 : 02000c08

Flags: nZCv IRQs off FIQs off Mode SVC_32 (T)

Code: b2c0 1c53 604b 7010 (4770) eef1

Resetting CPU ...

resetting ...

Debugging my app causes the "undefined instruction" message to be displayed and the resulting reset.

This is what I see when running the DE10-Nano factory image SD card:

U-Boot 2017.03-rc2 (Mar 30 2017 - 19:07:16 -0700)

CPU: Altera SoCFPGA Platform

FPGA: Altera Cyclone V, SE/A6 or SX/C6 or ST/D6, version 0x0

BOOT: SD/MMC Internal Transceiver (3.0V)

Watchdog enabled

I2C: ready

DRAM: 1 GiB

MMC: dwmmc0@ff704000: 0

*** Warning - bad CRC, using default environment

In: serial

Out: serial

Err: serial

Model: Terasic DE10-Nano

Net:

Error: ethernet@ff702000 address not set.

No ethernet found.

Hit any key to stop autoboot: 0

=>

When I start debugging my application no other characters are output and debugging works fine.

Any ideas? I'm stuck.

Thanks!

Brett

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brett

Did you by any chance make changes to the scatter file to point to the on chip ram?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Did you by any chance make changes to the scatter file to point to the on chip ram?

I assume you mean a scatter file to point to the SDRAM. Yes, I used an SDRAM scatter file and the document you linked to was the guide that I was following. I have copied the SDRAM scatter file contents below (it's identical to the one in the guide). Note that, as I mentioned in my original post, I am able to debug from SDRAM without issue if I load the bootloader from the factory DE10-Nano image first. The problems begin when I try using my build of U-Boot (to initialize the SDRAM prior to debugging).

scatter_SDRAM.scat:

SDRAM 0x02000000 0x02000000 ; 32M SDRAM

{

APP_CODE +0

{

* (+RO, +RW, +ZI)

}

ARM_LIB_STACKHEAP 0x03000000 EMPTY 0x01000000 ; Application heap and stack

{}

}

Thanks!

Brett

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brett

I see that you are running on the branch 2022.04.

Could you try out the branch for 2022.01?

2022.01 is the latest stable branch release.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the idea to try. Unfortunately, I am getting the same result using the 2022.01 branch.

U-Boot 2022.01-19547-g2544e805ea-dirty (Nov 10 2022 - 11:58:27 -0600)

CPU: Altera SoCFPGA Platform

FPGA: Altera Cyclone V, SE/A6 or SX/C6 or ST/D6, version 0x0

BOOT: SD/MMC Internal Transceiver (3.0V)

Watchdog enabled

DRAM: 1 GiB

MMC: dwmmc0@ff704000: 0

Loading Environment from MMC... *** Warning - bad CRC, using default environment

In: serial

Out: serial

Err: serial

Model: Altera SOCFPGA Cyclone V SoC Development Kit

Net:

Warning: ethernet@ff702000 (eth0) using random MAC address - 72:71:f8:f1:63:8e

eth0: ethernet@ff702000

Hit any key to stop autoboot: 0

=> undefined instruction

pc : [<02000bae>] lr : [<0200005f>]

reloc pc : [<c309cbee>] lr : [<c309c09f>]

sp : 03ffffe8 ip : 3ffe4248 fp : 02000bf8

r10: 02000bf8 r9 : 3bf61ed0 r8 : 00000000

r7 : 02000be7 r6 : 00000000 r5 : 00000000 r4 : 00000000

r3 : 00000000 r2 : 80000000 r1 : 02000d60 r0 : 02000c08

Flags: nZCv IRQs off FIQs off Mode SVC_32 (T)

Code: b2c0 1c53 604b 7010 (4770) eef1

Resetting CPU ...

resetting ...

Thanks,

Brett

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brett

Have you tried compiling and running the uboot version 2017.03-rc2 ?

Is it able to work?

Could you share me the file "socfpga_cyclone5_de10_nano"?

Could you point me the link where to get the uboot version of 2017.03-rc2?

Lets try to compare the u boot changes between the latest and 2017, starting from the config file.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Any update on this case?

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

>Have you tried compiling and running the uboot version 2017.03-rc2 ?

>Is it able to work?

I would have done this before even posting here if it made sense (and was possible). Unfortunately, this is not practical and would likely not reveal much. As described here, the U-Boot build flow changed considerably starting with SoC EDS Standard version 19.1. Furthermore, the U-Boot source code was integral to SoC EDS prior to this and later removed. To compile U-Boot 2017.03-rc2, I would have to locate an old version of SoC EDS Standard that contained U-Boot 2017.03-rc2. Then I would need to backdate my installation of SoC EDS to this version (rendering the current version unusable). Even if I could get to this step, the output would not be comparable to U-Boot 2022.01 since, according to everything I have read, there has been a number of under-the-hood changes to U-Boot between these releases.

>Could you share me the file "socfpga_cyclone5_de10_nano"?

The only files with this name that I could find have a dts and dtb extension. My understanding is that these are device tree files for Linux and thus not relevant to the current discussion.

In terms of building U-Boot, "socfpga_cyclone5_de10_nano" denotes a configuration, not a particular file. From what I can tell this configuration information is buried within some number of files scattered throughout the U-Boot project.

>Could you point me the link where to get the uboot version of 2017.03-rc2?

Your guess is probably better than mine as to where to find this. All I have is the SD Card image containing the prebuilt U-Boot files (https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&No=1046&PartNo=4).

>Lets try to compare the u boot changes between the latest and 2017, starting from the config file.

As stated above, this is not possible/practical or I would have done it already.

One new thing that I have discovered is that the example projects in HWLibs will run on the newer U-Boot releases (2022.04 and 2022.01). I should note that it is the GNU compiler versions that are working (I am unable to compile the ARMCC versions). So evidently there is something different in the startup code that makes these projects work and my Arm Compiler 6 project to not work.

So to recap as to what works and what doesn't:

| U-Boot Version | |||

| 2017.03-rc2 | 2022.04 | 2022.01 | |

| Bare-metal app - Arm Compiler 6 | YES | NO | NO |

| HWLibs demo app Altera-SoCFPGA-HardwareLib-Timer-CV-GNU |

YES | YES | YES |

Can anyone at Intel confirm that a bare-metal project compiled in Arm DS 2022.0 using Arm Compiler 6 can be succesfully executed on a recent release of U-Boot?

Thanks,

Brett

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brett

Sorry that I might ask some irrelevant question in my previous reply.

For CycloneV you should be using the Arm Compiler 5 which targets the Cortex-A9 on Cyclone V SoC,

Arria V SoC and Intel Arria 10 SoC.

The Arm Compiler 6 targets Cortex-A53 on Intel Stratix 10 SoC and Agilex SoC.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

@JingyangTeh_Altera wrote:For CycloneV you should be using the Arm Compiler 5 which targets the Cortex-A9 on Cyclone V SoC,

Arria V SoC and Intel Arria 10 SoC.

The Arm Compiler 6 targets Cortex-A53 on Intel Stratix 10 SoC and Agilex SoC.

Could you please point me to Intel literature that states this? It contradicts what I have found. On Intel's Arm Development Studio for Intel SoC FPGA webpage it states:

|

Compilers |

|

|

Arm Compiler 5 |

Included until Arm DS for Intel® SoC FPGA version 2020.1 |

|

Arm Compiler 6 |

Yes |

I cannot find anything stating that the current version of Arm DS (2022.0), which does not include Arm Compiler 5, should not to be used with Cyclone V, or that users need to downgrade to an Arm DS version from 3 years ago in order to have support for Cyclone V.

Granted, I realize that the HWLibs examples use GNU and Arm Compiler 5 and that they have not yet been updated to support Arm Compiler 6. But much/most of the Intel literature/examples/etc. is years out of date and not aligned with the current toolsets.

Again, I have no problem compiling and executing Arm Compiler 6 bare-metal applications from OCRAM, or SDRAM with U-Boot 2017-rc2. The problems are only with newer versions of U-Boot. I don't see how this is an Arm Compiler 6 problem. Something changed in U-Boot which is causing issues.

Thanks,

Brett

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

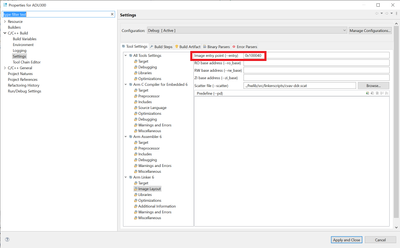

So I stumbled upon a fix. Explicitly setting the image entry point to 0x100040 eliminates the reset problem with U-Boot 2022.04 and I can debug my application normally. I have no idea why this problem only presents with newer versions of U-Boot.

Since Arm Compiler 6 was mentioned in this thread, I thought I should relay my experiences. (Arm Compiler 6 is the only compiler version that has been provided with Arm DS for Intel® SoC FPGA since 3 years back.) I have ported several of the HWLib examples to Arm Compiler 6 and they work fine. The only problems I have encountered so far relate to getting the environment set appropriately as much of the existing Intel documentation is years out of date. I ask that Intel please consider dedicating some resources to updating their documentation because as it sits the misalignment between the documentation and the current toolsets can lead to many hours of wasted time, particularly for new users of the platform such as myself.

Thanks,

Brett

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Brett

You could refer to the document

Intel® SoC FPGA Embedded Development Suite (SoC EDS) User Guide

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_soc_eds.pdf

Under section 9.1.

Sorry that you got a bad experience in the Intel Documents, I will try to the engineering team to update document.

This will help further enhance your experience in the future.

Regards

Jingyang, Teh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Since this thread been resolve, I shall set this thread to close pending. If you still need further assistance, you are welcome reopen this thread within 20days or open a new thread, some one will be right with you. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

If you happened to close this thread you might receive a survey. If you think you would rank your support experience less than 10 out of 10, please allow me to correct it before closing or if the problem can’t be corrected, please let me know the cause so that I may improve your future service experience.

Regards

Jingyang, Teh

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page