- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

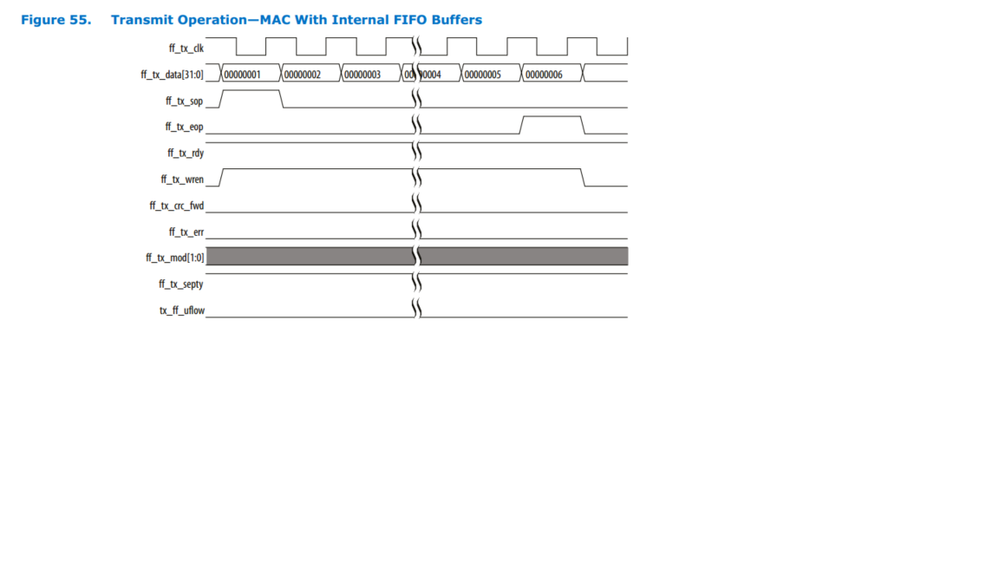

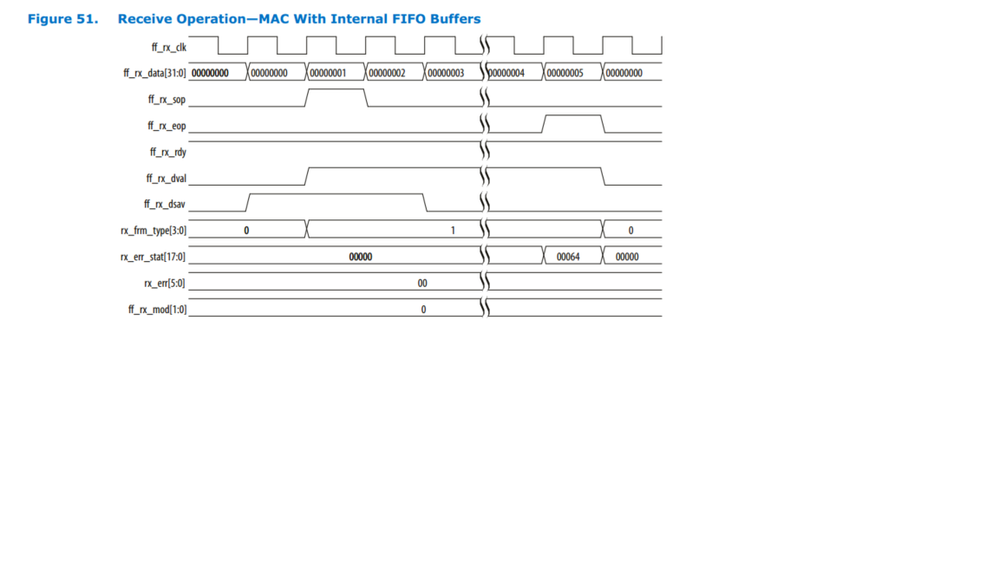

in TSE datasheet,the timing requirement about the data using by Avalon-ST interface.but the figure 51 and 55(shown below) confuse me.in Avalon-ST transmit interface as shown in figure 55,when should I change the data,in rising edge or falling edge of ff_tx_clk,or both?like figure 55,and in receive operation in figure 51,when should I read the data,as shown in figure,using falling edge of ff_rx_clk,but figure 51 and 55 using the different timing diagram.

Link Copied

1 Reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page