- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi all,

I have a max10 board, on which the JTAG pins should be used as normal IO. I found that, if a NIOS subsystem is initiated in my design, the fitter would complain about pin assignment confilict, even if the "JTAG pins sharing" option was checked.

Is it possible to use JTAG pins as IO with a NIOS processor presented?

and how?

best regards

Chao

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chao,

Enable JTAG pin sharing also read about JTAGEN

Please refer below link session 3.1 for Dual-Purpose Configuration Pins.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_config.pdf

Also please share below information.

- Can you post the pin assignment conflict message?

- Which Development Kit are you using?

- Quartus tool version used?

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thank you for your response.

I'm using our own board, not official development kit, and Quartus 15.

The fitter error messages are:

Error (176310): Can't place multiple pins assigned to pin location Pin_G1 (IOPAD_X10_Y17_N14)

Info (176311): Pin x1 is assigned to pin location Pin_G1 (IOPAD_X10_Y17_N14)

Info (176311): Pin altera_reserved_tms is assigned to pin location Pin_G1 (IOPAD_X10_Y17_N14)

Error (176310): Can't place multiple pins assigned to pin location Pin_G2 (IOPAD_X10_Y17_N21)

Info (176311): Pin x2 is assigned to pin location Pin_G2 (IOPAD_X10_Y17_N21)

Info (176311): Pin altera_reserved_tck is assigned to pin location Pin_G2 (IOPAD_X10_Y17_N21)

Error (176310): Can't place multiple pins assigned to pin location Pin_F5 (IOPAD_X10_Y16_N14)

Info (176311): Pin x3 is assigned to pin location Pin_F5 (IOPAD_X10_Y16_N14)

Info (176311): Pin altera_reserved_tdi is assigned to pin location Pin_F5 (IOPAD_X10_Y16_N14)

Error (176310): Can't place multiple pins assigned to pin location Pin_F6 (IOPAD_X10_Y16_N21)

Info (176311): Pin x4 is assigned to pin location Pin_F6 (IOPAD_X10_Y16_N21)

Info (176311): Pin altera_reserved_tdo is assigned to pin location Pin_F6 (IOPAD_X10_Y16_N21)

In my design, signal x1,x2,x3,x4 are single-endded ios.

If I removed the nios system .qsys file from my project, fitter didn't report any error.

In the max10 configuratin manual, it says "any JTAG-related IP cannot be used if you enable the JTAG pin sharing feature in your design".

So I believe the NIOS .qsys file must has JTAG-related IP in it.

Chao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chao,

Yes, we can't use The Signal Tap logic analyzer IP, JTAG-to-Avalon master bridge IP, and other JTAG-related IPs cannot be used if you enable the JTAG pin sharing feature in your design

.

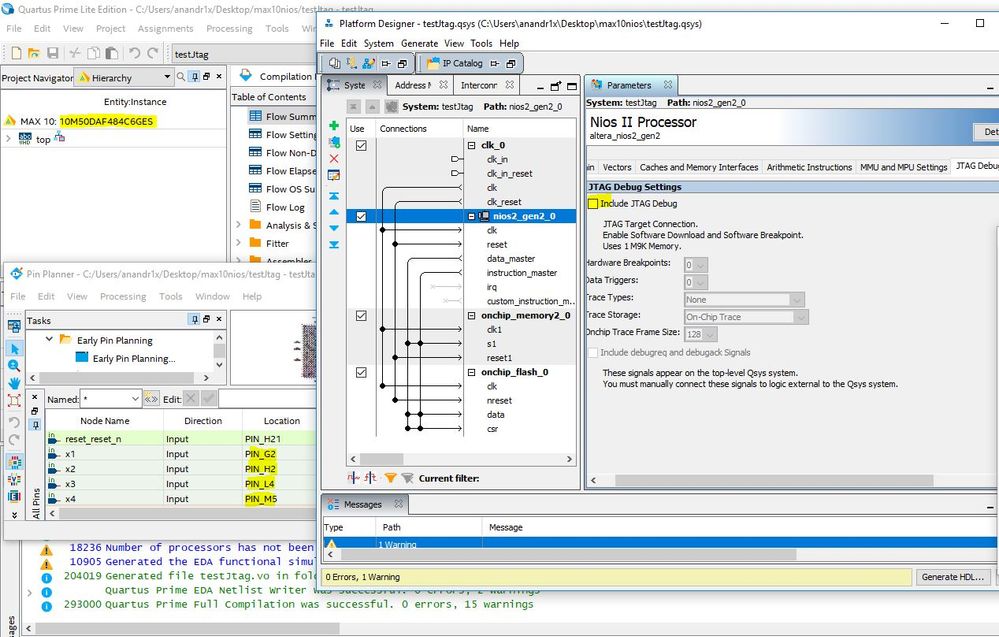

However, in Nios IP you can disable the JTAG debugger option and use it. Just remember that be can't download software and debug the system without the jtag debugger option.

I have checked it with a simple project, With Nios on-chip ram and flash IP's using Max 10 dev kit has a reference for my pin assignments.

Regards

Anand

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page