- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi support,

I am learning the simple socket server design on Cyclone 10 GX.

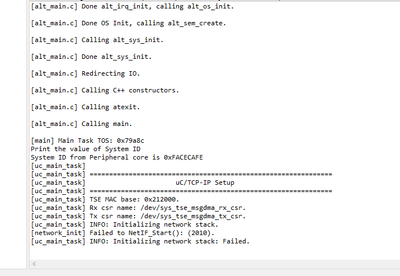

For unknown reason, the initialization process stopped with the error code (2010),

It's the TSE with DP83848.

The signals on MDIO and MDC is working.

Therefore I would like to know how to debug this issue.

Thank you.

BRs,

Johnson

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi

Did you managed to run the example design on the Cyclone10 EVB yet?

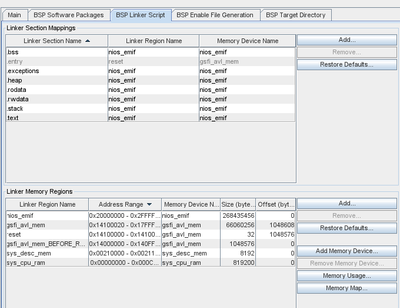

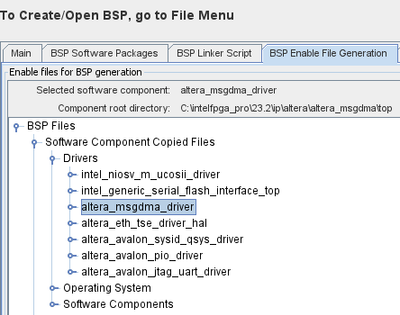

Please note the following setting when trying to generate the BSP for the application.

5.5.2.2. Configuring the BSP (intel.com)

For the application you could reuse the application code from the latest design example.

Regards

Jingyang, Teh

Link copiado

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

This case just got routed to me today.

May I know your setup? Are you directly connecting the board to your PC? If yes, then you may need to disable the "DHCP feature (!DEF_TRUE)":

Once you have set your IP address etc, rebuild the application and re-program the new .hex/.elf whichever you were using.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hello,

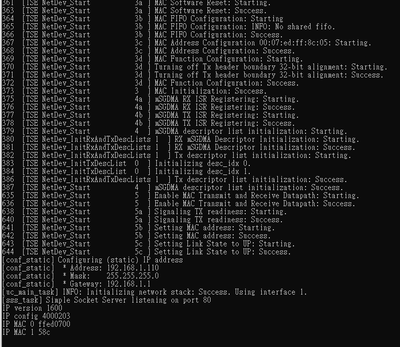

It's a custom board with C10 GX and DP83848.

We use Nios II with NicheStack in the past and are porting the Niso V now.

So the Hareware should be fine.

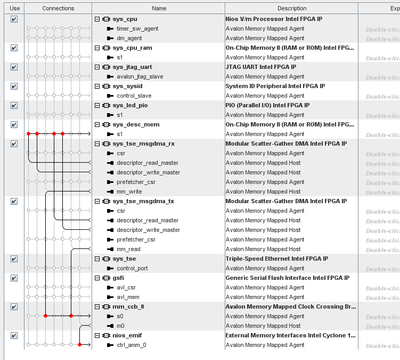

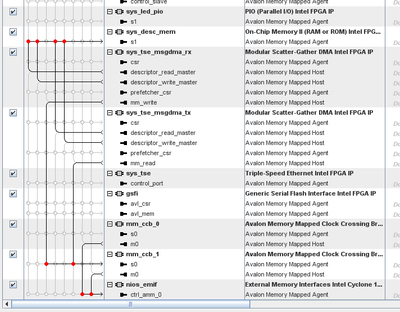

The qsys connection is like below.

The Nos V is running on EMIF.

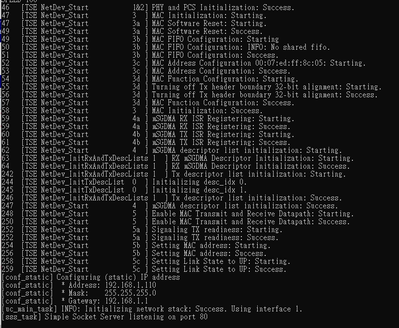

Following your instruction, the socket is running now.

But I can not connect to the server and ping to the specific is not responding..

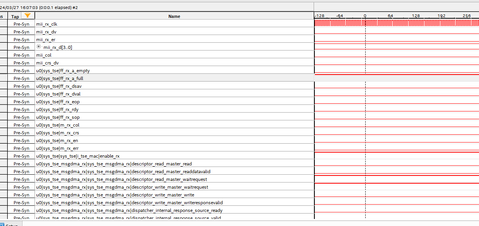

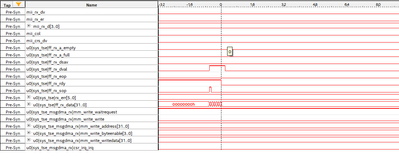

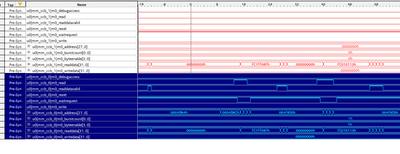

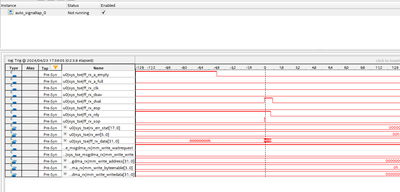

Form the STP, the ff_rx_a_full is always high.

I think there are problems on the FPGA side since the TSE IP is not responding..

BRs,

Johnson

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

Okay, we are moving in the correct direction, at least we can see what we can do next.

With the addresses now configure properly, and that the message “[sss_task] Simple Socket Server listening on port

<port number>” is displayed when the µC/TCP-IP Stack is ready for connection.

Can you show/screenshot on your Host PC's CMD, running below steps?:

After the µC/TCP-IP Stack is ready, you can start a telnet session to interact with the stack.

To start a telnet session, follow these steps:

1. From your operating system, open a command shell or a terminal.

Note: On Windows, you can also use Run on the Start menu.

2. Type the following command, specifying either the static IP address or the DHCPserver-provided IP address:

telnet <IP Address> <Port>

telnet 192.168.1.110 80

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

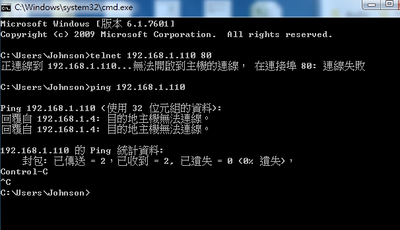

I tried telnet and ping command.

But no reply from the server

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

How is your setup? Does your computer (that is connected to the board) connected to a VPN or secure connection?

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi Eberlazare,

No, just through a switch.

And I am debugging the qsys..

I can see the mii_rx_d to TSE.

But for unknown reason, the ff_rx_a_full going high and ff_rx_rdy goes low after the SSS starting.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

I think the problem is the TSE not responding for unknown reason after the SSS running...

I STP the signals between TSE RX and the RX MSGDMA.

The ff_rx_rdy going low and not returned to high.

Perhaps something wrong on my Qsys setting or..

I feel the MSGDMA is not working and there's not much data about this IP..

I upload the QAR file for your analysis.

Thank you.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

Thanks, I will check out the design.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

What is the Quartus version that you are working on?

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

I am using Quartus Prime Pro 23.2.0 in Win 10.

Thank you.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

I may need some days to debug this issue, I shall update to you again in the next few days.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

From my findings, the signal issue you mentioned, it seems that it has something to do with some settings that need to be tweaked.

I will further investigate towards that and get back to you soon with some suggested workaround.

Thanks for your patience.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

Does the issue always have the "ff_rx_rdy" high? OR do you have it work at random times?

One of the workaround I could find was implementing a reset. I am not that familiar with the TSE IP, you could try to perform a reset signal:

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

From the STP content below, I think the ff_rx_rdy is a signal from DMA.

After downloading the sof and elf, the system booted with ff_rx_rdy high, which indicate to the core ready to receive data.

But it went low after with the network connected..

Therefore I guess there are problems on the msgdma ..

I read back some register settings on TSE core, and thought it should be configured correctly.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

I modify the design with Nios V to EMIF through a memory mapped clock crossing bridge and DMA through another bridge.

But for unknown reason the DMA bridge is not running...

I STP the bus and found only Nios V is running..

Any suggestions ? DMA driver or ...

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

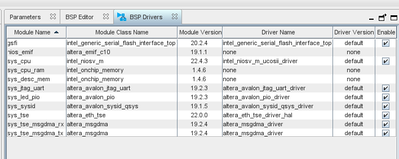

Hi,

Is the DMA & EMIF visible in the "drivers" tab in BSP-editor?

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

I believe so, as

and

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

Since we currently do not have the example for the Simple Socket Server with EMIF for Nios V, can you try with the OCRAM as per the Nios V handbook?:

Try with OCRAM, if it works then I can recommend to try with EMIF.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

I tried OCRMA before EMIF and it's not working for unknown reason.

I upload the QAR for your reference.

The STP content is the same as EMIF...

Perhaps some components are with wrong settings..

- Subscrever fonte RSS

- Marcar tópico como novo

- Marcar tópico como lido

- Flutuar este Tópico para o utilizador atual

- Marcador

- Subscrever

- Página amigável para impressora